100Gb/S QSFP28 1310nm 10km LR4 LC Dissendilo JHAQ28C10C

Trajtoj:

◊ 4 lenoj MUX/DEMUX-dezajno

◊ Integrita CWDM TOSA / ROSA por ĝis 10 km atingo super SMF

◊ Subtenu 100GBASE-CWDM4 por liniorapideco de 103.125Gbps kaj OTU4 por liniorapideco de 111.81Gbps

◊ Entuta bendolarĝo de > 100Gbps

◊ Duplex LC-konektiloj

◊ Konforme al IEEE 802.3-2012 Clause 88 normo IEEE 802.3bm CAUI-4 blato al modula elektra normo ITU-T G.959.1-2012-02 normo ·

◊ Ununura +3.3V nutrado funkcianta

◊ Enkonstruitaj ciferecaj diagnozaj funkcioj

◊ Temperaturintervalo 0 °C ĝis 70 °C

◊ RoHS Konforma Parto

Aplikoj:

◊ Loka Reto (LAN)

◊ Larĝa Area Reto (WAN)

◊ Ethernet-ŝaltiloj kaj enkursigiloj

Priskribo:

La JHAQ28C10C estas transceptora modulo desegnita por 10km optikaj komunikado-aplikoj.La dezajno konformas al 100GbASE-LR4 de la normo IEEE 802.3-2012 Clause 88 IEEE 802.3bm CAUI-4 blato al modula elektra normo ITU-T G.959.1-2012-02 normo.La modulo konvertas 4 enigajn kanalojn (ch) de 25.78 Gbps al 27.95Gbps elektraj datumoj al 4 lenoj optikaj signaloj, kaj multiplexas ilin en ununuran kanalon por 100Gb/s optika dissendo.Inverse, ĉe la ricevilo, la modulo optike de-multipleksas 100Gb/s enigaĵon en 4 lenojn signalojn, kaj transformas ilin al 4 lenoj eligas elektrajn datenojn.

La centraj ondolongoj de la 4 lenoj estas 1270 Nm, 1290 Nm, 1310 Nm kaj 1330 Nm.Ĝi enhavas dupleksa LC-konektilo por la optika interfaco kaj 38-stifta konektilo por la elektra interfaco.Por minimumigi la optikan disvastiĝon en la longdistanca sistemo, unureĝima fibro (SMF) devas esti aplikita en ĉi tiu modulo.

La produkto estas desegnita kun formofaktoro, optika/elektra konekto kaj cifereca diagnoza interfaco laŭ la QSFP28 Plurfonta Interkonsento (MSA).Ĝi estis desegnita por renkonti la plej severajn eksterajn funkciajn kondiĉojn inkluzive de temperaturo, humideco kaj EMI-interfero.

La modulo funkcias de ununura +3.3V nutrado kaj LVCMOS/LVTTL tutmondaj kontrolsignaloj kiel Modulo Present, Reset, Interrompo kaj Malalta Potenca Reĝimo estas haveblaj kun la moduloj.2-drata seria interfaco disponeblas por sendi kaj ricevi pli kompleksajn kontrolsignalojn kaj akiri ciferecajn diagnozajn informojn.Individuaj kanaloj povas esti traktitaj kaj neuzataj kanaloj povas esti fermitaj por maksimuma dezajnofleksebleco.

La JHAQ28C10C estas desegnita kun formofaktoro, optika/elektra konekto kaj cifereca diagnoza interfaco laŭ la QSFP28 Plurfonta Interkonsento (MSA).Ĝi estis desegnita por renkonti la plej severajn eksterajn funkciajn kondiĉojn inkluzive de temperaturo, humideco kaj EMI-interfero.La modulo ofertas tre altan funkciecon kaj funkcion integriĝon, alireblan per dudrata seria interfaco.

•Absolutaj Maksimumaj Taksoj

| Parametro | Simbolo | Min. | Tipa | Maks. | Unuo |

| Tenada Temperaturo | TS | —40 |

| +85 | °C |

| Proviza Tensio | VCCT, R | -0,5 |

| 4 | V |

| Relativa Humideco | RH | 0 |

| 85 | % |

•RekomenditaOperacia Medio:

| Parametro | Simbolo | Min. | Tipa | Maks. | Unuo |

| Kazo funkcianta Temperaturo | TC | 0 |

| +70 | °C |

| Proviza Tensio | VCCT, R | +3.13 | 3.3 | +3.47 | V |

| Proviza Fluo | ICC |

| 1100 | 1500 | mA |

| Potenco Dissipado | PD |

|

| 5 | W |

•Elektraj Karakterizaĵoj(TOP = 0 ĝis 70 °C, VCC = 3,13 ĝis 3,47 Voltoj

| Parametro | Simbolo | Min | Tip | Maks | Unuo | Notu | ||

| Datumkurso por Kanalo |

| - | 25.78125 |

| Gbps |

| ||

|

|

| 27.9525 |

|

| ||||

| Energikonsumo |

| - | 2.7 | 3.5 | W |

| ||

| Proviza Fluo | Icc |

| 0.8 | 1 | A |

| ||

| Kontrolo I/O Tensio-Alta | VIH | 2.0 |

| Vcc | V |

| ||

| Kontrolo I/O Tensio-Malalta | VIL | 0 |

| 0.7 | V |

| ||

| Inter-kanala Skew | TSK |

|

| 35 | Ps |

| ||

| RESETL Daŭro |

|

| 10 |

| Us |

| ||

| RESETL De-aserti tempon |

|

|

| 100 | ms |

| ||

| Power On Time |

|

|

| 100 | ms |

| ||

| Dissendilo | ||||||||

| Ununura Finita Eliga Tensio-Toleremo |

| 0.3 |

| Vcc | V | 1 | ||

| Komuna reĝimo Tensio-Toleremo |

| 15 |

|

| mV |

| ||

| Transdono de Eniga Diftensio | VI | 150 |

| 1200 | mV |

| ||

| Transdona Eniga Difimpedanco | ZIN | 85 | 100 | 115 |

|

| ||

| Datuma Dependa Eniga Tremo | DDJ |

| 0.3 |

| UI |

| ||

| Ricevilo | ||||||||

| Ununura Finita Eliga Tensio-Toleremo |

| 0.3 |

| 4 | V |

| ||

| Rx Eligo Diff Tensio | Vo | 370 | 600 | 950 | mV |

| ||

| Rx Eligo Pliiĝo kaj Falita Tensio | Tr/Tf |

|

| 35 | ps | 1 | ||

| Tuta Jitter | TJ |

| 0.3 |

| UI |

| ||

Notu:

- 20~80%

•Optikaj Parametroj (TOP = 0 ĝis 70°C, VCC = 3,0 ĝis 3,6 Voltoj)

| Parametro | Simbolo | Min | Tip | Maks | Unuo | Ref. | ||

| Dissendilo | ||||||||

| Ondolonga Asigno | L0 | 1264.5 | 1271 | 1277.5 | nm |

| ||

| L1 | 1284.5 | 1291 | 1297.5 | nm |

| |||

| L2 | 1304.5 | 1311 | 1317.5 | nm |

| |||

| L3 | 1324.5 | 1331 | 1337.5 | nm |

| |||

| Flankreĝima Subprema Proporcio | SMSR | 30 | - | - | dB |

| ||

| Totala Meza Lanĉa Potenco | PT | -6 | - | 6.5 | dBm |

| ||

| Meza Lanĉpovo, ĉiu Leno |

| -6 | - | 2.5 | dBm |

| ||

| Diferenco en Lanĉpotenco inter iuj du Lenoj (OMA) |

| - | - | 3.5 | dB |

| ||

| TDP, ĉiu Leno | TDP |

|

| 2.2 | dB |

| ||

| Formorta Proporcio | ER | 4 | - | - | dB | |||

| Dissendilo Okula Masko Difino {X1, X2, X3, Y1, Y2, Y3} |

| {0.25, 0.4, 0.45, 0.25, 0.28, 0.4} |

| |||||

| Optika Revena Perdo-Toleremo |

| - | - | 20 | dB |

| ||

| Averaĝa Lanĉa Power OFF Dissendilo, ĉiu Leno | Kapelo |

|

| -30 | dBm |

| ||

| Relativa Intensa Bruo | Rin |

|

| —128 | dB/HZ | 1 | ||

| Optika Revena Perdo-Toleremo |

| - | - | 12 | dB |

| ||

| Ricevilo | ||||||||

| Damaĝo Sojlo | THd | 3.3 |

|

| dBm | 1 | ||

| Meza Potenco ĉe Ricevilo-Enigo, ĉiu Leno | R | -13.0 |

| 0 | dBm |

| ||

| RSSI-Precizeco |

| -2 |

| 2 | dB |

| ||

| Ricevilo Reflektado | Rrx |

|

| -26 | dB |

| ||

| Receiver Power (OMA), ĉiu Leno |

| - | - | 3.5 | dBm |

| ||

| LOS De-Aserto | LOSD |

|

| -15 | dBm |

| ||

| LOS Asert | LOSA | -25 |

|

| dBm |

| ||

| LOS-Histerezo | LOSH | 0.5 |

|

| dB |

| ||

Notu

- 12dB Reflektado

•Diagnoza Monitorada Interfaco

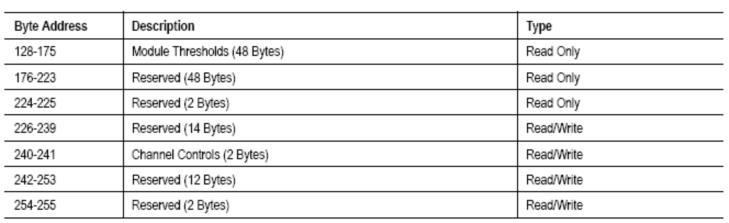

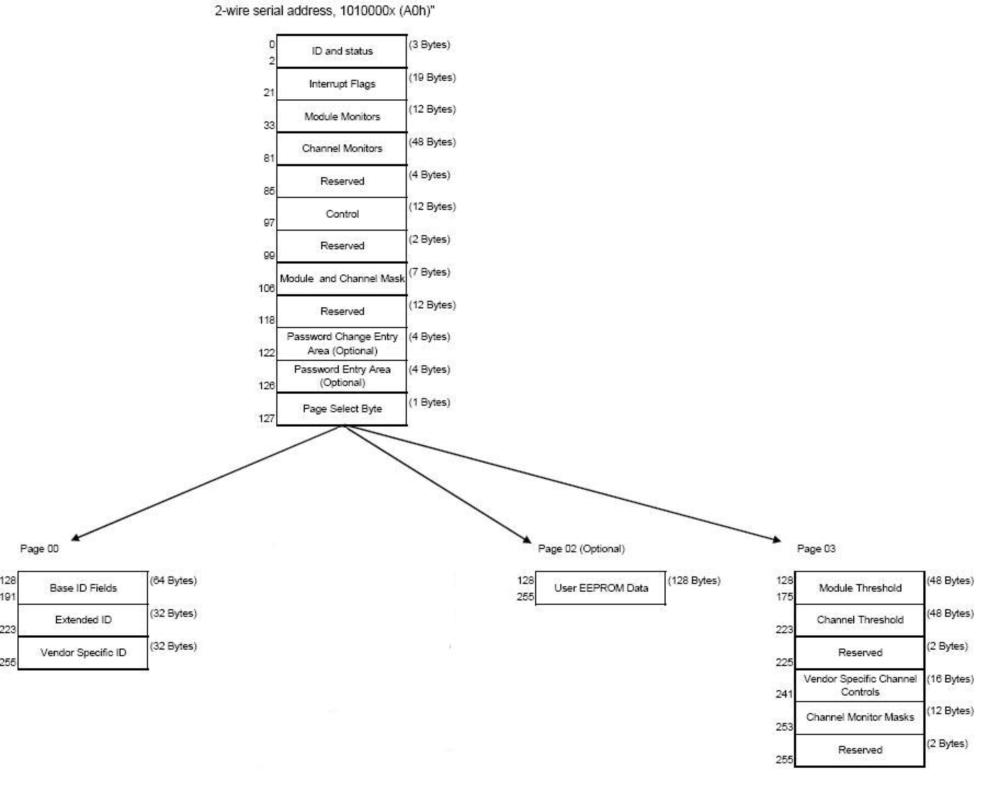

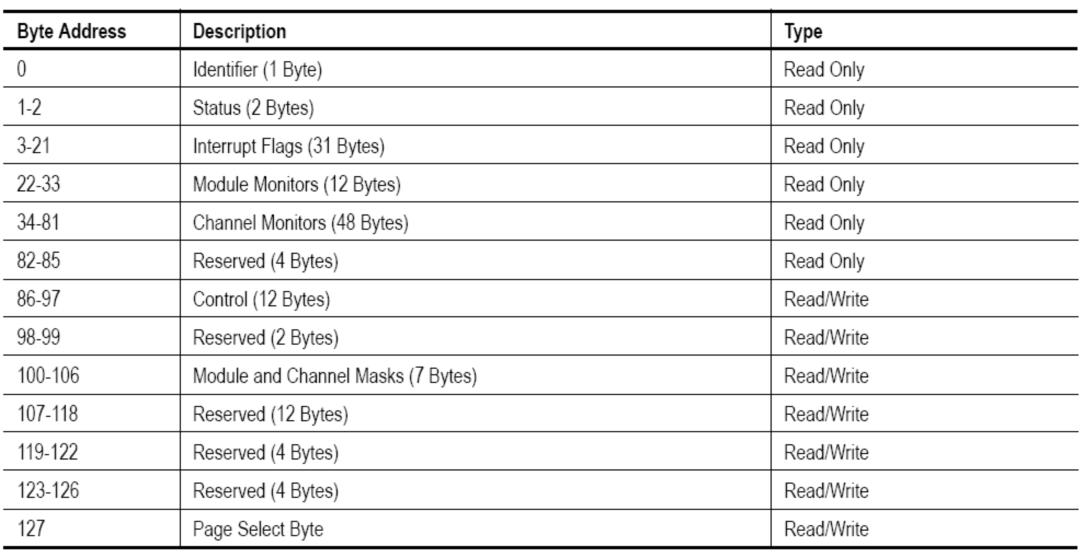

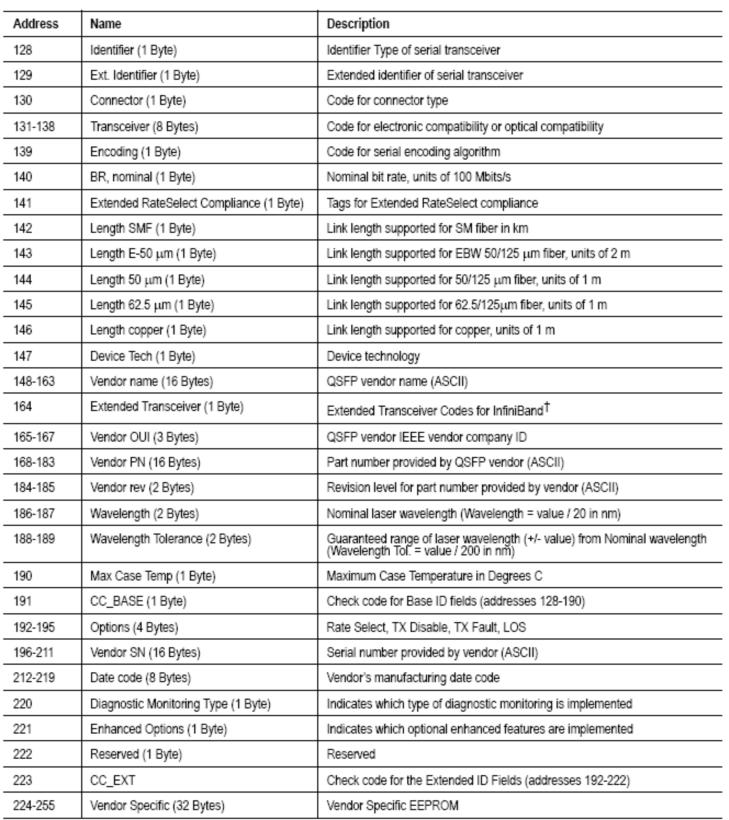

Cifereca diagnoza monitora funkcio estas havebla sur ĉiuj QSFP28 LR4.2-drata seria interfaco provizas uzanton por kontakti modulon.La strukturo de la memoro montriĝas en fluado.La memorspaco estas aranĝita en pli malaltan, ununuran paĝon, adresspacon de 128 bajtoj kaj multoblajn suprajn adresspaĝojn.Ĉi tiu strukturo permesas ĝustatempan aliron al adresoj en la malsupra paĝo, kiel Interrupt Flagoj kaj Monitoroj.Malpli tempaj kritikaj tempo-enskriboj, kiel seriaj ID-informoj kaj sojlaj agordoj, estas disponeblaj per la funkcio Page Select.La interfacadreso uzata estas A0xh kaj estas ĉefe uzata por tempaj kritikaj datumoj kiel interrompa uzado por ebligi unufojan legadon por ĉiuj datumoj rilataj al interrompa situacio.Post interrompo, IntL estis asertita, la gastiganto povas legi la flagkampon por determini la tuŝitan kanalon kaj specon de flago.

Paĝo02 estas Uzanto-EEPROM kaj ĝia formato decidas de uzanto.

La detala priskribo de malalta memoro kaj page00.page03 supra memoro bonvolu vidi SFF-8436-dokumenton.

•Tempo por Soft Kontrolo kaj Statusaj Funkcioj

| Parametro | Simbolo | Maks | Unuo | Kondiĉoj |

| Komenca Tempo | t_init | 2000 | ms | Tempo de ŝaltado1, varma ŝtopilo aŭ altiĝanta rando de Restarigi ĝis la modulo plene funkcias2 |

| Restarigi Init Asert Time | t_reset_init | 2 | μs | Reset estas generita per malalta nivelo pli longa ol la minimuma rekomencigita pulstempo ĉeestanta sur la ResetL-stifto. |

| Seria Busa Aparataro Preta Tempo | t_serialo | 2000 | ms | Tempo de ŝaltado1 ĝis modulo respondas al transdono de datumoj per la 2-drata seria buso |

| Monitoro Datumoj PretaTempo | t_datenoj | 2000 | ms | Tempo de ŝaltado1 ĝis datumoj ne preta, bito 0 de Bajto 2, senvalorigita kaj IntL asertita |

| Restarigi Aserti Tempon | t_restarigi | 2000 | ms | Tempo de leviĝanta rando sur la ResetL-pinglo ĝis la modulo plene funkcia2 |

| LPMode Asert Time | ton_LPMode | 100 | μs | Tempo de aserto de LPMode (Vin:LPMode =Vih) ĝis modula elektrokonsumo eniras pli malaltan Potencnivelon |

| IntL Asert Time | ton_IntL | 200 | ms | Tempo de okazo de kondiĉo ekiganta IntL ĝis Vout:IntL = Vol |

| IntL Deassert Time | toff_IntL | 500 | μs | toff_IntL 500 μs Tempo de malplenigo de read3 operacio de rilata flago ĝis Vout:IntL = Voh.Ĉi tio inkluzivas desertajn tempojn por Rx LOS, Tx Fault kaj aliaj flagpecoj. |

| Rx LOS Asert Time | ton_los | 100 | ms | Tempo de Rx LOS-ŝtato ĝis Rx LOS-bitaro kaj IntL asertis |

| Flago Aserti Tempon | ton_flago | 200 | ms | Tempo de okazo de kondiĉo ekiganta flago al rilata flagbitaro kaj IntL asertis |

| Masko Aserta Tempo | ton_masko | 100 | ms | Tempo de masko bito set4 ĝis rilata IntL-aserto estas malhelpita |

| Masko De-aserti Tempon | toff_mask | 100 | ms | Tempo de masko bito malbarita4 ĝis asociita IntlL operacio rekomencas |

| ModSelL Asert Time | ton_ModeloL | 100 | μs | Tempo de aserto de ModSelL ĝis modulo respondas al transdono de datumoj per la 2-drata seria buso |

| ModSelL Deassert Time | toff_ModSelL | 100 | μs | Tempo de desenigo de ModSelL ĝis la modulo ne respondas al datumtranssendo super la 2-drata seria buso |

| Power_over-ride aŭPotenco-aro Asert Time | ton_Pdown | 100 | ms | Tempo de P_Down-bitaro 4 ĝis modula elektrokonsumo eniras pli malaltan Potencnivelon |

| Power_over-ride aŭ Power-set De-asert Time | toff_Pdown | 300 | ms | Tempo de P_Down malbarita4 ĝis la modulo plene funkcia3 |

Notu:

1. Potenco estas difinita kiel la momento kiam provizotensioj atingas kaj restas ĉe aŭ super la minimuma specifita valoro.

2. Plene funkcia estas difinita kiel IntL asertita pro datumoj ne pretaj bito, bito 0 bajto 2 de-asertita.

3. Mezurita de falanta horloĝo rando post halto bito de legita transakcio.

4. Mezurita de falanta horloĝa rando post halto skriba transakcio.

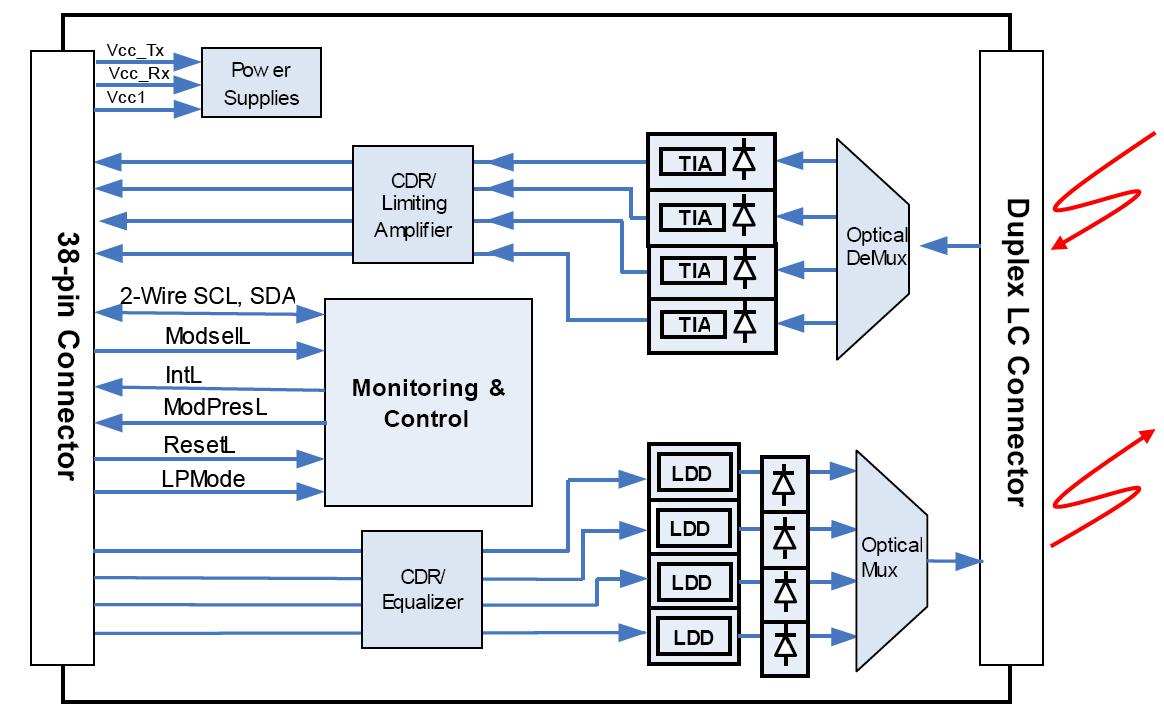

•Transceptora Blokdiagramo

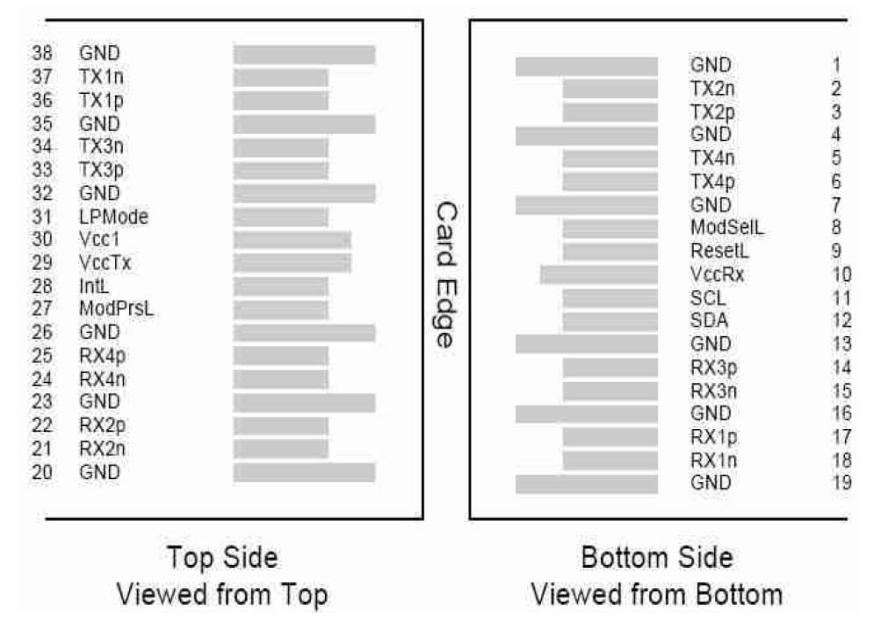

•Pinta Asigno

Diagramo de Gastiganta Estraro Konektilo Bloko Pinglo-Nombroj kaj Nam

•PingloPriskribo

| Pinglo | Logiko | Simbolo | Nomo/Priskribo | Ref. |

| 1 |

| GND | Tero | 1 |

| 2 | CML-I | Tx2n | Transsendilo Inversa Datuma Enigo |

|

| 3 | CML-I | Tx2p | Dissendilo Ne-Inversa Datuma eligo |

|

| 4 |

| GND | Tero | 1 |

| 5 | CML-I | Tx4n | Transsendilo Inversa Datuma Eligo |

|

| 6 | CML-I | Tx4p | Dissendilo Ne-Inversa Datuma Eligo |

|

| 7 |

| GND | Tero | 1 |

| 8 | LVTTL-I | ModSelL | Elektu Modulon |

|

| 9 | LVTTL-I | Restarigi L | Restarigi modulon |

|

| 10 |

| VccRx | +3.3V Elektroprovizo Ricevilo | 2 |

| 11 | LVCMOS-I/O | SCL | 2-drata Seria Interfaco Horloĝo |

|

| 12 | LVCMOS-I/O | SDA | 2-Drata Seria Interfaco-Datumoj |

|

| 13 |

| GND | Tero | 1 |

| 14 | CML-O | Rx3p | Ricevilo Invertita Datuma Eligo |

|

| 15 | CML-O | Rx3n | Ricevilo Ne-Inversa Datuma Eligo |

|

| 16 |

| GND | Tero | 1 |

| 17 | CML-O | Rx1p | Ricevilo Invertita Datuma Eligo |

|

| 18 | CML-O | Rx1n | Ricevilo Ne-Inversa Datuma Eligo |

|

| 19 |

| GND | Tero | 1 |

| 20 |

| GND | Tero | 1 |

| 21 | CML-O | Rx2n | Ricevilo Invertita Datuma Eligo |

|

| 22 | CML-O | Rx2p | Ricevilo Ne-Inversa Datuma Eligo |

|

| 23 |

| GND | Tero | 1 |

| 24 | CML-O | Rx4n | Ricevilo Invertita Datuma Eligo |

|

| 25 | CML-O | Rx4p | Ricevilo Ne-Inversa Datuma Eligo |

|

| 26 |

| GND | Tero | 1 |

| 27 | LVTTL-O | ModPrsL | Modulo Presente |

|

| 28 | LVTTL-O | IntL | Interrompi |

|

| 29 |

| VccTx | +3.3V Elektroprovizo-Dissendilo | 2 |

| 30 |

| Vcc1 | +3.3V Elektroprovizo | 2 |

| 31 | LVTTL-I | LPMode | Malalta Potenca Reĝimo |

|

| 32 |

| GND | Tero | 1 |

| 33 | CML-I | Tx3p | Transsendilo Inversa Datuma Eligo |

|

| 34 | CML-I | Tx3n | Dissendilo Ne-Inversa Datuma Eligo |

|

| 35 |

| GND | Tero | 1 |

| 36 | CML-I | Tx1p | Transsendilo Inversa Datuma Eligo |

|

| 37 | CML-I | Tx1n | Dissendilo Ne-Inversa Datuma Eligo |

|

| 38 |

| GND | Tero | 1 |

Notoj:

- GND estas la simbolo por unuopaĵo kaj provizo(potenco) ofta por QSFP28-moduloj, Ĉiuj estas oftaj ene de la QSFP28-modulo kaj ĉiuj modulaj tensioj estas referencitaj al ĉi tiu potencialo alie notitaj.Konektu ĉi tiujn rekte al la gastiganta tabulo signala komuna grunda ebeno.Lasera eligo malebligita sur TDIS >2.0V aŭ malfermita, ebligita sur TDIS <0.8V.

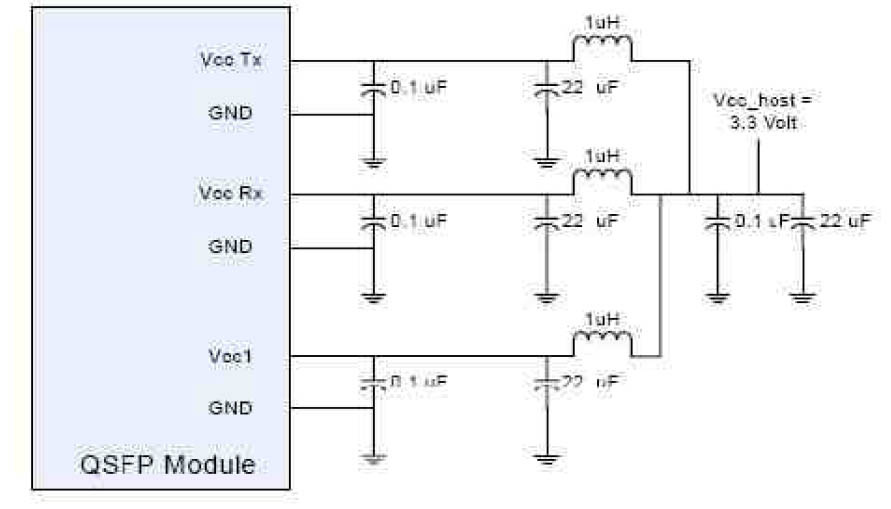

- VccRx, Vcc1 kaj VccTx estas la riceviloj kaj dissendilaj elektroprovizantoj kaj devas esti aplikataj samtempe.Rekomendita filtrado de elektroprovizo de gastiganta tabulo estas montrita sube.VccRx, Vcc1 kaj VccTx povas esti interne ligitaj ene de la QSFP28-elsendilomodulo en iu kombinaĵo.La konektilstiftoj estas ĉiu taksita por maksimuma fluo de 500mA.

•Rekomendita Cirkvito

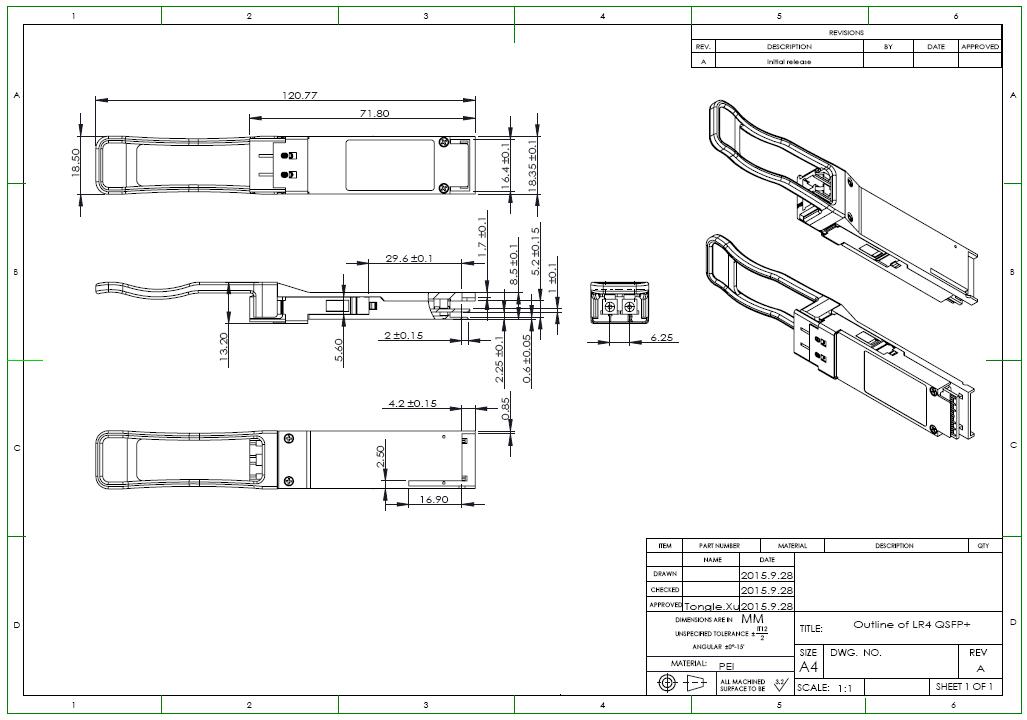

•Mekanikaj Dimensioj