100Gb/S QSFP28 1310nm 10km LR4 LC Transceiver JHAQ28C10C

Mga Tampok:

◊ 4 na lane na MUX/DEMUX na disenyo

◊ Pinagsamang CWDM TOSA / ROSA para sa hanggang 10 km na abot sa SMF

◊ Suportahan ang 100GBASE-CWDM4 para sa line rate na 103.125Gbps at OTU4 para sa line rate na 111.81Gbps

◊ Pinagsama-samang bandwidth na > 100Gbps

◊ Duplex LC connectors

◊ Sumusunod sa IEEE 802.3-2012 Clause 88 standard IEEE 802.3bm CAUI-4 chip to module electrical standard ITU-T G.959.1-2012-02 standard ·

◊ Single +3.3V power supply na tumatakbo

◊ Mga built-in na digital diagnostic function

◊ Saklaw ng temperatura 0°C hanggang 70°C

◊ Bahagi ng RoHS Compliant

Mga Application:

◊ Local Area Network (LAN)

◊ Wide Area Network (WAN)

◊ Ethernet switch at router application

Paglalarawan:

Ang JHAQ28C10C ay isang transceiver module na idinisenyo para sa 10km optical communication applications.Ang disenyo ay sumusunod sa 100GbASE-LR4 ng IEEE 802.3-2012 Clause 88 standard IEEE 802.3bm CAUI-4 chip to module electrical standard ITU-T G.959.1-2012-02 standard .Ang module ay nagko-convert ng 4 na input channel (ch) ng 25.78 Gbps hanggang 27.95Gbps na electrical data sa 4 na lane na optical signal, at pina-multiply ang mga ito sa iisang channel para sa 100Gb/s optical transmission.Sa kabaligtaran, sa gilid ng receiver, optically de-multiplexes ng module ang isang 100Gb/s input sa 4 na lane signal, at kino-convert ang mga ito sa 4 na lane na output ng electrical data.

Ang mga gitnang wavelength ng 4 na lane ay 1270 nm, 1290 nm, 1310 nm at 1330 nm .Naglalaman ito ng duplex LC connector para sa optical interface at isang 38-pin connector para sa electrical interface.Upang mabawasan ang optical dispersion sa long-haul system, kailangang ilapat ang single-mode fiber (SMF) sa module na ito.

Ang produkto ay dinisenyo na may form factor, optical/electrical na koneksyon at digital diagnostic interface ayon sa QSFP28 Multi-Source Agreement (MSA).Ito ay idinisenyo upang matugunan ang pinakamahirap na panlabas na kondisyon ng pagpapatakbo kabilang ang temperatura, halumigmig at pagkagambala ng EMI.

Ang module ay gumagana mula sa isang +3.3V power supply at ang LVCMOS/LVTTL global control signal tulad ng Module Present, Reset, Interrupt at Low Power Mode ay available kasama ng mga module.Available ang 2-wire serial interface para magpadala at tumanggap ng mas kumplikadong mga control signal at makakuha ng digital diagnostic information.Maaaring matugunan ang mga indibidwal na channel at maaaring isara ang mga hindi nagamit na channel para sa maximum na flexibility ng disenyo.

Ang JHAQ28C10C ay dinisenyo na may form factor, optical/electrical na koneksyon at digital diagnostic interface ayon sa QSFP28 Multi-Source Agreement (MSA).Ito ay idinisenyo upang matugunan ang pinakamahirap na panlabas na kondisyon ng pagpapatakbo kabilang ang temperatura, halumigmig at pagkagambala ng EMI.Nag-aalok ang module ng napakataas na functionality at feature integration, na naa-access sa pamamagitan ng two-wire serial interface.

•Ganap na Pinakamataas na Mga Rating

| Parameter | Simbolo | Min. | Karaniwan | Max. | Yunit |

| Temperatura ng Imbakan | TS | -40 |

| +85 | °C |

| Supply Boltahe | VCCT, R | -0.5 |

| 4 | V |

| Kamag-anak na Humidity | RH | 0 |

| 85 | % |

•InirerekomendaOperating Environment:

| Parameter | Simbolo | Min. | Karaniwan | Max. | Yunit |

| Temperatura ng pagpapatakbo ng kaso | TC | 0 |

| +70 | °C |

| Supply Boltahe | VCCT, R | +3.13 | 3.3 | +3.47 | V |

| Kasalukuyang Supply | ICC |

| 1100 | 1500 | mA |

| Pagkawala ng kapangyarihan | PD |

|

| 5 | W |

•Mga katangiang elektrikal(TOP = 0 hanggang 70 °C, VCC = 3.13 hanggang 3.47 Volts

| Parameter | Simbolo | Min | Typ | Max | Yunit | Tandaan | ||

| Rate ng Data bawat Channel |

| - | 25.78125 |

| Gbps |

| ||

|

|

| 27.9525 |

|

| ||||

| Konsumo sa enerhiya |

| - | 2.7 | 3.5 | W |

| ||

| Kasalukuyang Supply | Icc |

| 0.8 | 1 | A |

| ||

| Kontrolin ang I/O Voltage-Mataas | VIH | 2.0 |

| Vcc | V |

| ||

| Kontrolin ang I/O Voltage-Mababa | VIL | 0 |

| 0.7 | V |

| ||

| Inter-Channel Skew | TSK |

|

| 35 | Ps |

| ||

| Tagal ng RESETL |

|

| 10 |

| Us |

| ||

| RESETL I-de-assert ang oras |

|

|

| 100 | ms |

| ||

| Power On Time |

|

|

| 100 | ms |

| ||

| Tagapaghatid | ||||||||

| Single Ended Output Voltage Tolerance |

| 0.3 |

| Vcc | V | 1 | ||

| Common mode Voltage Tolerance |

| 15 |

|

| mV |

| ||

| Magpadala ng Input Diff Voltage | VI | 150 |

| 1200 | mV |

| ||

| Magpadala ng Input Diff Impedance | ZIN | 85 | 100 | 115 |

|

| ||

| Data Dependent Input Jitter | DDJ |

| 0.3 |

| UI |

| ||

| Receiver | ||||||||

| Single Ended Output Voltage Tolerance |

| 0.3 |

| 4 | V |

| ||

| Rx Output Diff Voltage | Vo | 370 | 600 | 950 | mV |

| ||

| Pagtaas at Pagbagsak ng Boltahe ng Output ng Rx | Tr/Tf |

|

| 35 | ps | 1 | ||

| Kabuuang Jitter | TJ |

| 0.3 |

| UI |

| ||

Tandaan:

- 20~80%

•Mga Optical Parameter(TOP = 0 hanggang 70°C, VCC = 3.0 hanggang 3.6 Volts)

| Parameter | Simbolo | Min | Typ | Max | Yunit | Ref. | ||

| Tagapaghatid | ||||||||

| Takdang-aralin sa wavelength | L0 | 1264.5 | 1271 | 1277.5 | nm |

| ||

| L1 | 1284.5 | 1291 | 1297.5 | nm |

| |||

| L2 | 1304.5 | 1311 | 1317.5 | nm |

| |||

| L3 | 1324.5 | 1331 | 1337.5 | nm |

| |||

| Side-mode Suppression Ratio | SMSR | 30 | - | - | dB |

| ||

| Kabuuang Average na Lakas ng Paglunsad | PT | -6 | - | 6.5 | dBm |

| ||

| Average na Lakas ng Paglunsad, bawat Lane |

| -6 | - | 2.5 | dBm |

| ||

| Pagkakaiba sa Launch Power sa pagitan ng alinmang dalawang Lanes (OMA) |

| - | - | 3.5 | dB |

| ||

| TDP, bawat Lane | TDP |

|

| 2.2 | dB |

| ||

| Extinction Ratio | ER | 4 | - | - | dB | |||

| Transmitter Eye Mask Definition {X1, X2, X3, Y1, Y2, Y3} |

| {0.25, 0.4, 0.45, 0.25, 0.28, 0.4} |

| |||||

| Optical Return Loss Tolerance |

| - | - | 20 | dB |

| ||

| Average na Paglunsad ng Power OFF Transmitter, bawat Lane | Poff |

|

| -30 | dBm |

| ||

| Relatibong Intensity Ingay | Rin |

|

| -128 | dB/HZ | 1 | ||

| Optical Return Loss Tolerance |

| - | - | 12 | dB |

| ||

| Receiver | ||||||||

| Threshold ng Pinsala | THd | 3.3 |

|

| dBm | 1 | ||

| Average na Power sa Receiver Input, bawat Lane | R | -13.0 |

| 0 | dBm |

| ||

| Katumpakan ng RSSI |

| -2 |

| 2 | dB |

| ||

| Receiver Reflectance | Rrx |

|

| -26 | dB |

| ||

| Receiver Power (OMA), bawat Lane |

| - | - | 3.5 | dBm |

| ||

| LOS De-Assert | LOSD |

|

| -15 | dBm |

| ||

| Iginiit ng LOS | LOSA | -25 |

|

| dBm |

| ||

| LOS Hysteresis | LOSH | 0.5 |

|

| dB |

| ||

Tandaan

- 12dB Reflection

•Diagnostic Monitoring Interface

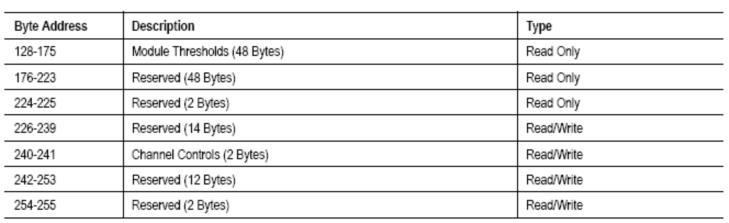

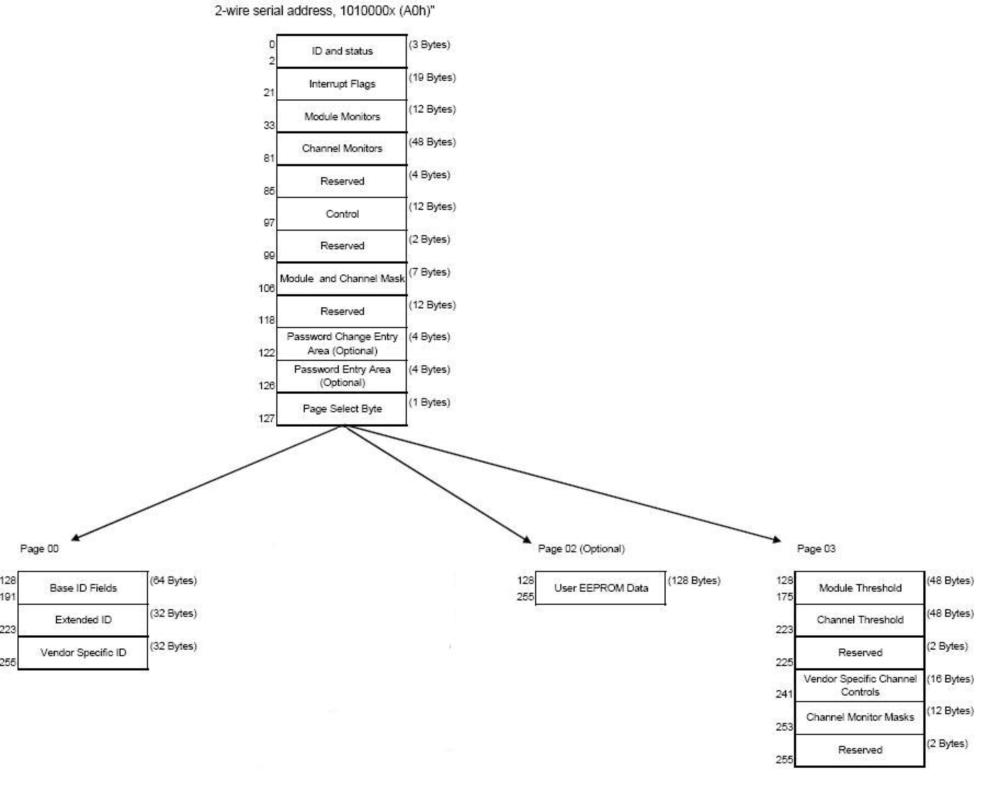

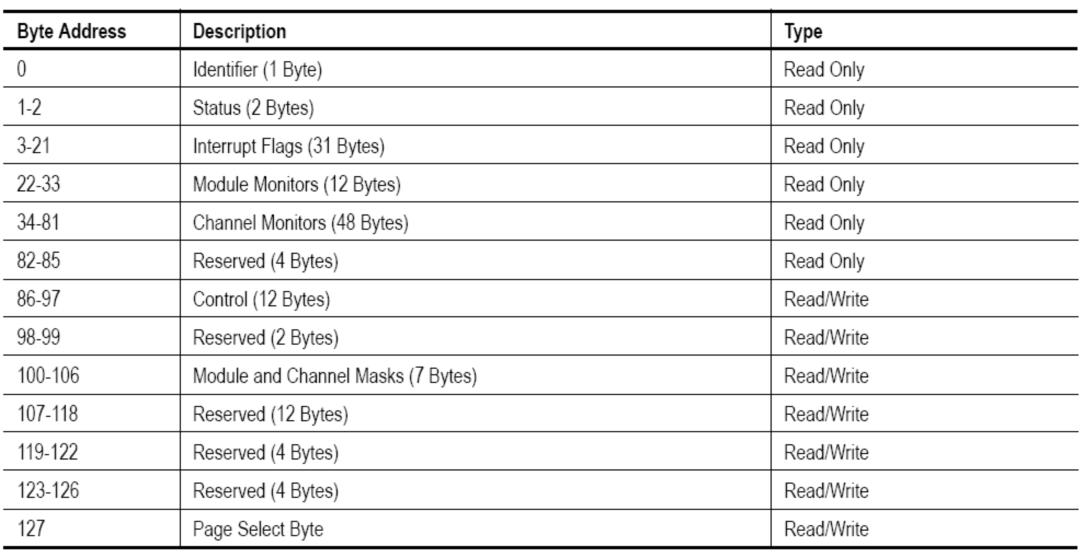

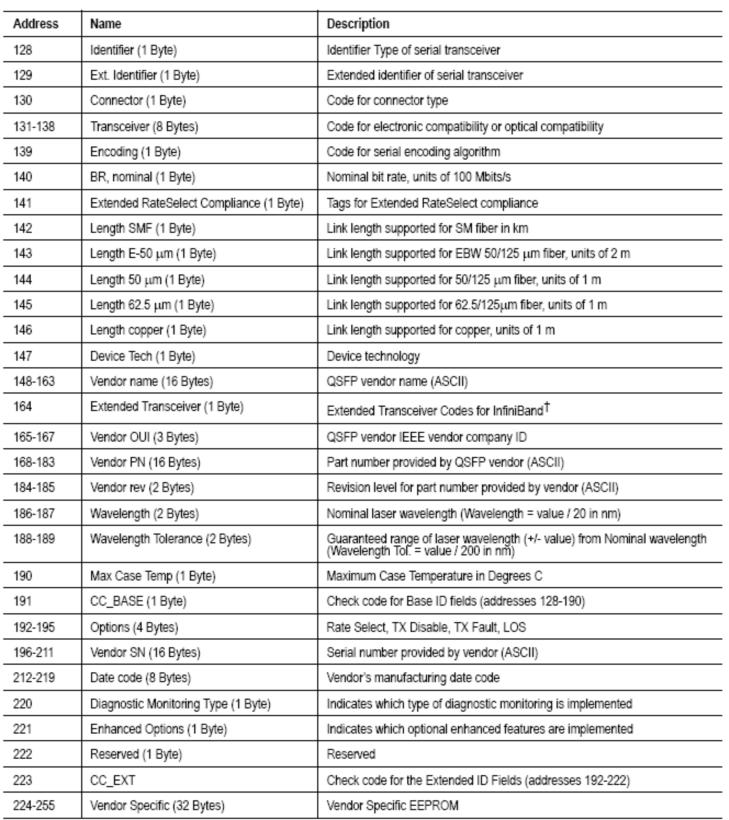

Available ang digital diagnostics monitoring function sa lahat ng QSFP28 LR4.Ang isang 2-wire serial interface ay nagbibigay ng user upang makipag-ugnayan sa module.Ang istraktura ng memorya ay ipinapakita sa daloy.Ang memory space ay nakaayos sa isang mas mababang, solong pahina, address space na 128 bytes at maramihang mga upper address space na pahina.Ang istrukturang ito ay nagbibigay-daan sa napapanahong pag-access sa mga address sa ibabang pahina, tulad ng Interrupt Flag at Monitor.Ang mas kaunting oras na mga entry sa kritikal na oras, tulad ng impormasyon ng serial ID at mga setting ng threshold, ay available sa function na Page Select.Ang interface address na ginamit ay A0xh at pangunahing ginagamit para sa oras na kritikal na data tulad ng interrupt handling upang paganahin ang isang beses na basahin para sa lahat ng data na nauugnay sa isang interrupt na sitwasyon.Pagkatapos ng interrupt, iginiit ng IntL, mababasa ng host ang flag field para matukoy ang apektadong channel at uri ng flag.

Ang Page02 ay User EEPROM at ang format nito ay napagpasyahan ng user.

Ang detalyadong paglalarawan ng mababang memorya at page00.page03 itaas na memorya mangyaring tingnan ang dokumentong SFF-8436.

•Timing para sa Soft Control at Status Function

| Parameter | Simbolo | Max | Yunit | Mga kundisyon |

| Oras ng Pagsisimula | t_init | 2000 | ms | Oras mula sa power on1, mainit na plug o tumataas na gilid ng I-reset hanggang sa ganap na gumana ang module2 |

| I-reset ang Init Assert Time | t_reset_init | 2 | μs | Ang isang Reset ay nabuo sa pamamagitan ng isang mababang antas na mas mahaba kaysa sa minimum na reset pulse time na nasa ResetL pin. |

| Oras ng Handa ng Serial Bus Hardware | t_serial | 2000 | ms | Oras mula sa power on1 hanggang tumugon ang module sa paghahatid ng data sa 2-wire serial bus |

| Subaybayan ang Data HandaOras | t_data | 2000 | ms | Oras mula sa power on1 hanggang sa data na hindi pa handa, bit 0 ng Byte 2, deasserted at IntL asserted |

| I-reset ang Assert Time | t_reset | 2000 | ms | Oras mula sa pagtaas ng gilid sa ResetL pin hanggang sa ganap na gumagana ang module2 |

| LPMode Assert Time | ton_LPMode | 100 | μs | Oras mula sa paggigiit ng LPMode (Vin:LPMode =Vih) hanggang sa ang pagkonsumo ng kuryente ng module ay pumasok sa mas mababang Power Level |

| IntL Assert Time | ton_IntL | 200 | ms | Oras mula sa paglitaw ng kundisyong nagti-trigger ng IntL hanggang Vout:IntL = Vol |

| Oras ng IntL Deassert | toff_IntL | 500 | μs | toff_IntL 500 μs Oras mula sa clear sa read3 na operasyon ng nauugnay na flag hanggang Vout:IntL = Voh.Kabilang dito ang mga oras ng deassert para sa Rx LOS, Tx Fault at iba pang flag bits. |

| Rx LOS Assert Time | tonelada_los | 100 | ms | Oras mula sa Rx LOS state hanggang Rx LOS bit set at iginiit ng IntL |

| Flag Assert Time | tonelada_flag | 200 | ms | Oras mula sa paglitaw ng kundisyon na nagti-trigger ng flag hanggang sa nauugnay na flag bit set at iginiit ng IntL |

| Oras ng Mask Assert | ton_mask | 100 | ms | Oras mula sa mask bit set4 hanggang sa ang nauugnay na IntL assertion ay inhibited |

| Oras ng Pag-alis ng Mask | toff_mask | 100 | ms | Oras mula sa mask bit cleared4 hanggang sa nauugnay na operasyon ng IntlL na magpapatuloy |

| Oras ng Pagpapahayag ng ModSelL | ton_ModSelL | 100 | μs | Oras mula sa paggigiit ng ModSelL hanggang sa tumugon ang module sa paghahatid ng data sa 2-wire na serial bus |

| Oras ng Deassert ng ModSelL | toff_ModSelL | 100 | μs | Oras mula sa deassertion ng ModSelL hanggang sa hindi tumugon ang module sa paghahatid ng data sa 2-wire serial bus |

| Power_over-ride oPower-set Assert Time | tonelada_Pdown | 100 | ms | Oras mula sa P_Down bit set 4 hanggang ang module power consumption ay pumasok sa mas mababang Power Level |

| Power_over-ride o Power-set De-assert Time | toff_Pdown | 300 | ms | Oras mula P_Down bit cleared4 hanggang sa ang module ay ganap na gumagana3 |

Tandaan:

1. Ang power on ay tinukoy bilang ang instant kapag umabot ang mga boltahe ng supply at nananatili sa o higit pa sa minimum na tinukoy na halaga.

2. Ang fully functional ay tinukoy bilang IntL asserted dahil sa data not ready bit, bit 0 byte 2 de-asserted.

3. Sinusukat mula sa bumabagsak na gilid ng orasan pagkatapos huminto ng kaunting nabasang transaksyon.

4. Sinusukat mula sa bumabagsak na gilid ng orasan pagkatapos ng stop bit ng write transaction.

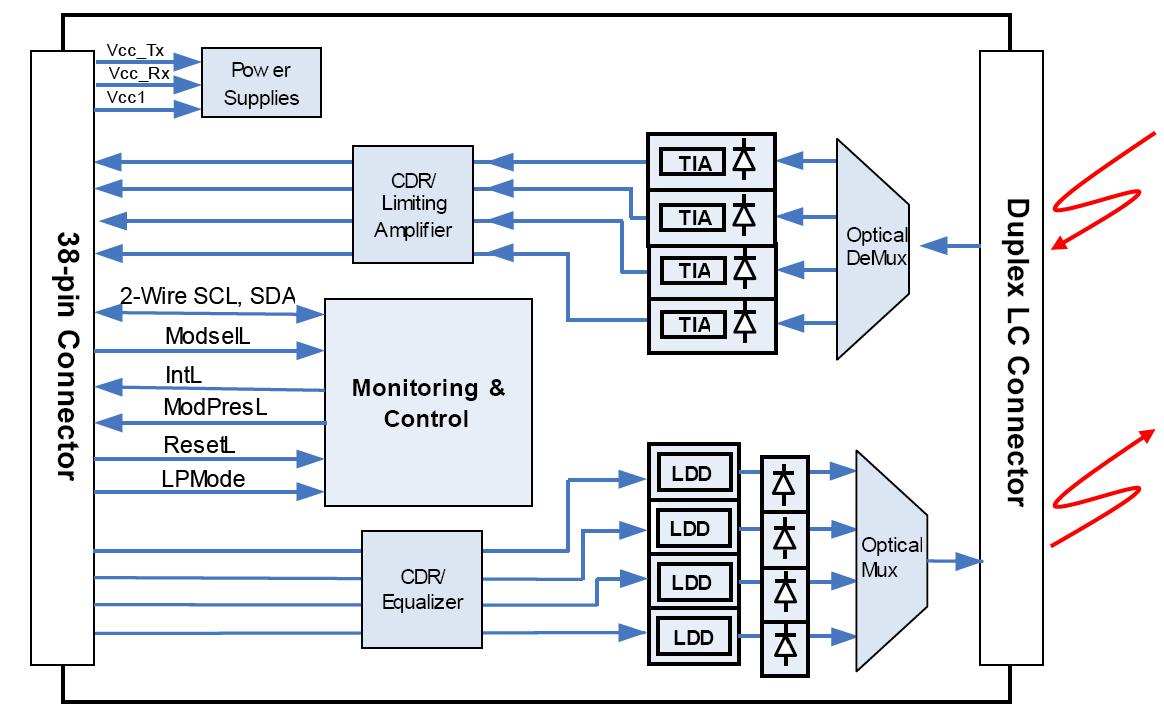

•Transceiver Block Diagram

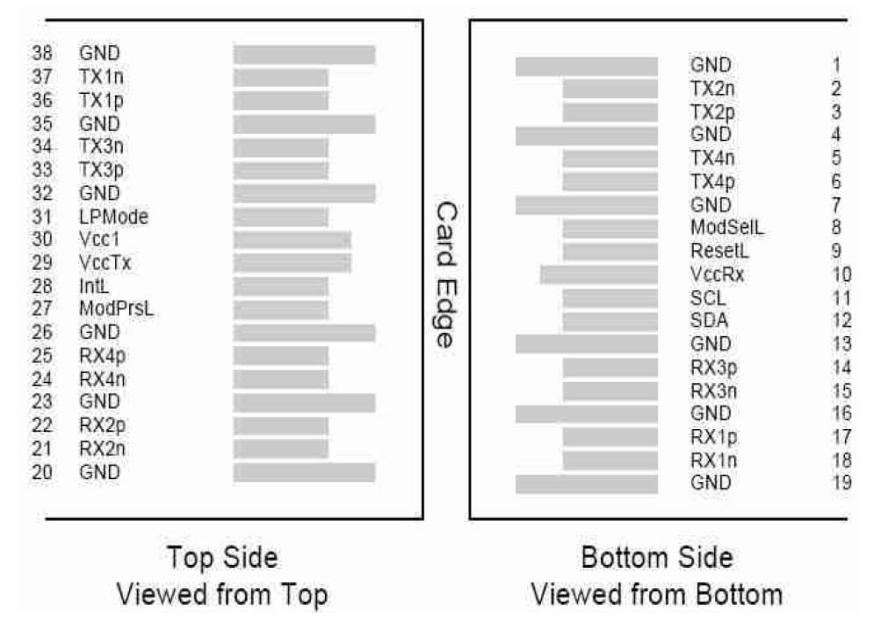

•Pin Assignment

Diagram ng Host Board Connector Block Pin Numbers at Nam

•PinPaglalarawan

| Pin | Lohika | Simbolo | Pangalan/Paglalarawan | Ref. |

| 1 |

| GND | Lupa | 1 |

| 2 | CML-I | Tx2n | Transmitter Inverted Data Input |

|

| 3 | CML-I | Tx2p | Transmitter Non-Inverted Data output |

|

| 4 |

| GND | Lupa | 1 |

| 5 | CML-I | Tx4n | Transmitter Inverted Data Output |

|

| 6 | CML-I | Tx4p | Transmitter Non-Inverted Data Output |

|

| 7 |

| GND | Lupa | 1 |

| 8 | LVTTL-I | ModSelL | Piliin ang Module |

|

| 9 | LVTTL-I | I-resetL | I-reset ang Module |

|

| 10 |

| VccRx | +3.3V Power Supply Receiver | 2 |

| 11 | LVCMOS-I/O | SCL | 2-Wire Serial Interface Clock |

|

| 12 | LVCMOS-I/O | SDA | 2-Wire Serial Interface Data |

|

| 13 |

| GND | Lupa | 1 |

| 14 | CML-O | Rx3p | Receiver Inverted Data Output |

|

| 15 | CML-O | Rx3n | Receiver Non-Inverted Data Output |

|

| 16 |

| GND | Lupa | 1 |

| 17 | CML-O | Rx1p | Receiver Inverted Data Output |

|

| 18 | CML-O | Rx1n | Receiver Non-Inverted Data Output |

|

| 19 |

| GND | Lupa | 1 |

| 20 |

| GND | Lupa | 1 |

| 21 | CML-O | Rx2n | Receiver Inverted Data Output |

|

| 22 | CML-O | Rx2p | Receiver Non-Inverted Data Output |

|

| 23 |

| GND | Lupa | 1 |

| 24 | CML-O | Rx4n | Receiver Inverted Data Output |

|

| 25 | CML-O | Rx4p | Receiver Non-Inverted Data Output |

|

| 26 |

| GND | Lupa | 1 |

| 27 | LVTTL-O | ModPrsL | Module Present |

|

| 28 | LVTTL-O | IntL | Makagambala |

|

| 29 |

| VccTx | +3.3V Power Supply Transmitter | 2 |

| 30 |

| Vcc1 | +3.3V Power Supply | 2 |

| 31 | LVTTL-I | LPMode | Mababang Power Mode |

|

| 32 |

| GND | Lupa | 1 |

| 33 | CML-I | Tx3p | Transmitter Inverted Data Output |

|

| 34 | CML-I | Tx3n | Transmitter Non-Inverted Data Output |

|

| 35 |

| GND | Lupa | 1 |

| 36 | CML-I | Tx1p | Transmitter Inverted Data Output |

|

| 37 | CML-I | Tx1n | Transmitter Non-Inverted Data Output |

|

| 38 |

| GND | Lupa | 1 |

Mga Tala:

- Ang GND ay ang simbolo para sa single at supply(power) na karaniwan para sa QSFP28 modules, Lahat ay karaniwan sa loob ng QSFP28 module at lahat ng module voltages ay tinutukoy sa potensyal na ito kung hindi man nabanggit.Direktang ikonekta ang mga ito sa host board signal common ground plane.Naka-disable ang laser output sa TDIS >2.0V o bukas, naka-enable sa TDIS <0.8V.

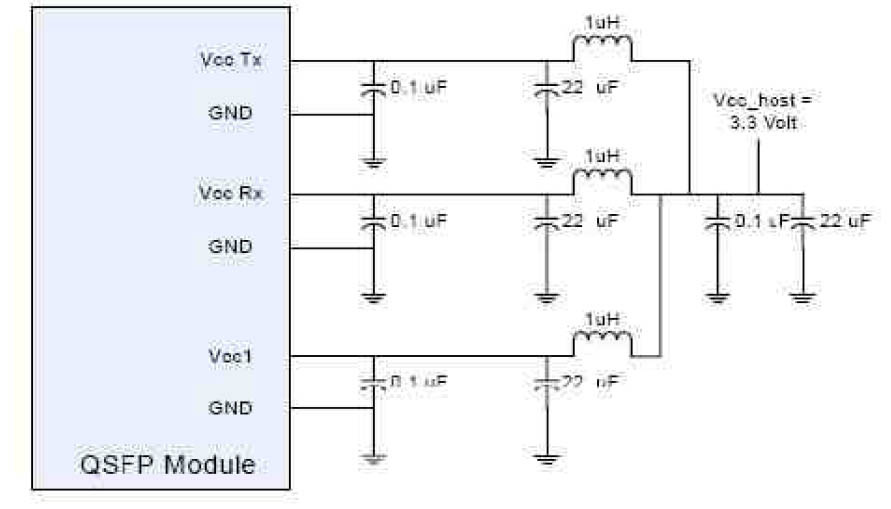

- Ang VccRx, Vcc1 at VccTx ay ang receiver at transmitter power supplier at dapat ilapat nang sabay-sabay.Ang inirerekomendang host board power supply filtering ay ipinapakita sa ibaba.Ang VccRx, Vcc1 at VccTx ay maaaring panloob na konektado sa loob ng QSFP28 transceiver module sa anumang kumbinasyon.Ang mga connector pin ay bawat isa ay na-rate para sa pinakamataas na kasalukuyang ng 500mA.

•Inirerekomendang Circuit

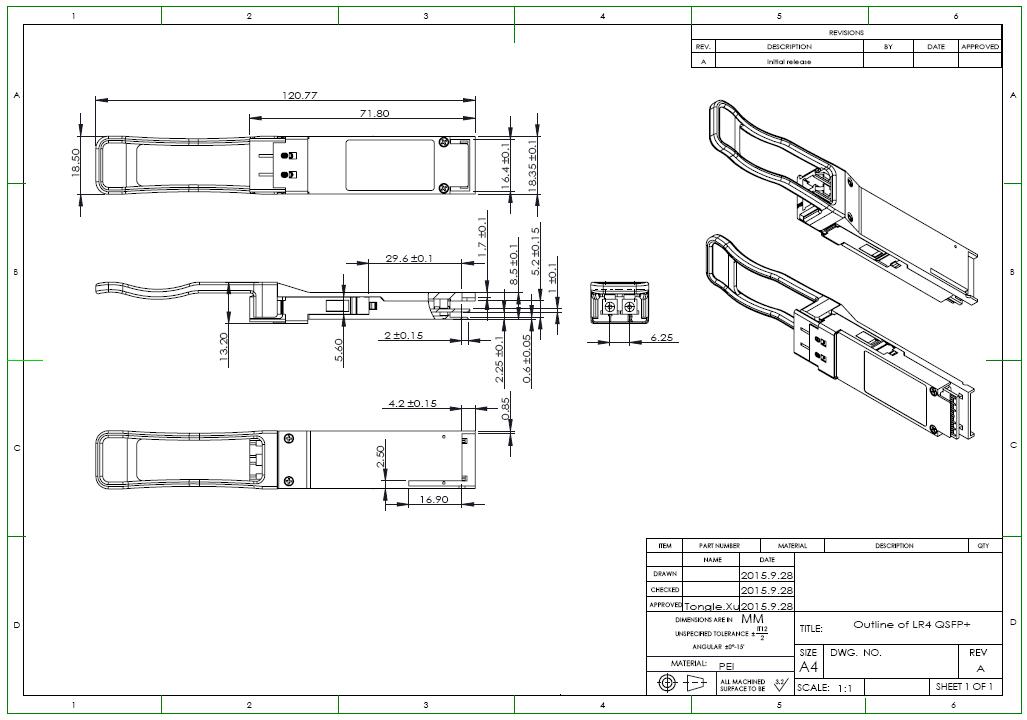

•Mga Dimensyon ng Mekanikal