40G Q/4SFP+ Direct Attach Kabel JHA-QSFP-40G-PCU

Allgemeng Beschreiwung

QSFP+ Direct Attach Kabele sinn kompatibel mat de SFF-8436 Spezifikatioune.SFP+ Direct Attach Kabele sinn kompatibel mat den SFF-8431, SFF-8432 an SFF-8472 Spezifikatioune.Verschidde Choixen vun Drot Jauge sinn verfügbar vun 30 bis 24 AWG mat verschiddene Wiel vu Kabellängt (bis zu 7m).

Eegeschaften

◊ Kompatibel mat SFF-8436, SFF-8431, SFF-8432 an SFF-8472

◊ Bis zu 10. 3125Gbps Datenrate pro Kanal

◊ Bis zu 7m Iwwerdroung

◊ Operatiounstemperatur: -40 ℃ bis +80 ℃

◊ Single 3.3V Stroumversuergung

◊ RoHS konform

Virdeeler

◊ Kënschtlech Kupferléisung

◊ Niddregsten Total System Muecht Léisung

◊ Niddregsten Gesamtsystem EMI Léisung

◊ Optimiséiert Design fir Signal Integritéit

Uwendungen

◊ 40G Ethernet

Spezifizéierung

Pin Funktioun Definitioun

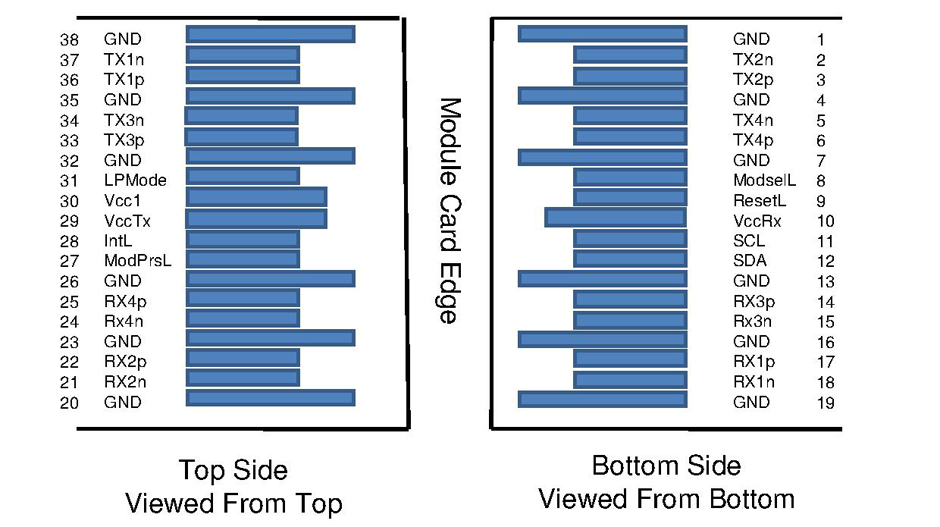

QSFP + Pin Funktioun Definitioun

| Pin | Logik | Symbol | Beschreiwung |

| 1 |

| GND | Buedem |

| 2 | CML-I | tx2n | Sender Inverted Data Input |

| 3 | CML-I | tx2p | Sender Non-Inverted Data Input |

| 4 |

| GND | Buedem |

| 5 | CML-I | tx4n | Sender Inverted Data Input |

| 6 | CML-I | tx4p | Sender Non-Inverted Data Input |

| 7 |

| GND | Buedem |

| 8 | LVTTL-I | ModSel | Modul Wielt |

| 9 | LVTTL-I | Reset L | Modul zréckgesat |

| 10 |

| Vcc Rx | +3.3V Power Supply Receiver |

| 11 | LVCMOS- I/O | SCL | 2-Drot Serien Interface Auer |

| 12 | LVCMOS- I/O | SDA | 2-Drot Serien Interface Daten |

| 13 |

| GND | Buedem |

| 14 | CML-O | rx3p | Receiver Non-Inverted Data Output |

| 15 | CML-O | rx3 n | Empfänger Inverted Data Output |

| 16 |

| GND | Buedem |

| 17 | CML-O | rx1p | Receiver Non-Inverted Data Output |

| 18 | CML-O | rx1n | Empfänger Inverted Data Output |

| 19 |

| GND | Buedem |

| 20 |

| GND | Buedem |

| 21 | CML-O | rx2n | Empfänger Inverted Data Output |

| 22 | CML-O | rx2p | Receiver Non-Inverted Data Output |

| 23 |

| GND | Buedem |

| 24 | CML-O | rx4n | Empfänger Inverted Data Output |

| 25 | CML-O | rx4p | Receiver Non-Inverted Data Output |

| 26 |

| GND | Buedem |

| 27 | LVTTL-O | ModPrsL | Modul Present |

| 28 | LVTTL-O | IntL | Ënnerbriechung |

| 29 |

| Vcc Tx | +3.3V Stroumversuergung Sender |

| 30 |

| vcc1 | +3,3V Stroumversuergung |

| 31 | LVTTL-I | LPMode | Low Power Modus |

| 32 |

| GND | Buedem |

| 33 | CML-I | tx3p | Sender Non-Inverted Data Input |

| 34 | CML-I | tx3n | Sender Inverted Data Input |

| 35 |

| GND | Buedem |

| 36 | CML-I | tx1p | Sender Non-Inverted Data Input |

| 37 | CML-I | tx1n | Sender Inverted Data Input |

| 38 |

| GND | Buedem |

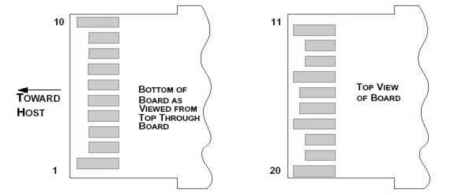

SFP+ Pin Funktioun Definitioun

| Pin | Logik | Symbol | Beschreiwung |

| 1 | VeeT | Modul Sender Ground | |

| 2 | LVTTL-O | Tx_Fault | Modul Sender Feeler |

| 3 | LVTTL-I | Tx_Desaktivéieren | Sender auszeschalten;Schalt de Sender Laserausgang aus |

| 4 | LVTTL-I/O | SDA | 2-Drot Serial Interface Data Line (Selwecht wéi MOD-DEF2 an INF-8074i) |

| 5 | LVTTL-I/O | SCL | 2-Drot Serial Interface Auer (Selwecht wéi MOD-DEF1 an INF-8074i) |

| 6 | Mod_ABS | Modul Absent, verbonne mat VeeT oder VeeR am Modul | |

| 7 | LVTTL-I | RS0 | Taux Wielt 0, fakultativ Kontrollen SFP + Modul Receiver |

| 8 | LVTTL-O | Rx_LOS | Empfänger Verloscht vum Signal Indikatioun (Am FC bezeechent als Rx_LOS an an Ethernet bezeechent als Signal Detect) |

| 9 | LVTTL-I | RS1 | Taux Wielt 1, kontrolléiert optional SFP + Modul Sender |

| 10 | VeR | Modul Receiver Ground | |

| 11 | VeR | Modul Receiver Ground | |

| 12 | CML-O | RD- | Empfänger Inverted Data Output |

| 13 | CML-O | RD+ | Receiver Non-Inverted Data Output |

| 14 | VeR | Modul Receiver Ground | |

| 15 | VccR | Modul Receiver 3,3 V Fourniture | |

| 16 | VccT | Modul Sender 3,3 V Fourniture | |

| 17 | VeeT | Modul Sender Ground | |

| 18 | CML-I | TD+ | Sender Non-Inverted Data Input |

| 19 | CML-I | TD- | Sender Inverted Data Input |

| 20 | VeeT | Modul Sender Ground |

Général Produit Charakteristiken

| Q/4SFP+ DAC Spezifikatioune | |

| Zuel vun Bunnen | Tx & Rx |

| Channel Data Taux | 10,3125 Gbps |

| Operatioun Temperatur | 0 bis +70°C |

| Späichertemperatur | -40 bis +85°C |

| Versuergung Volt | 3,3 V nominell |

| Elektresch Interface | 38 Pins Randverbindung (QSFP+)20 Pins Randverbindung (SFP+)

|

| Management Interface | Serien, I2C |

Héich Speed Charakteristiken

| Parameter | Symbol | Min | Typ | Max | Unitéiten | Notizen |

| Differentialimpedanz | Zd | 90 | 100 | 110 | Ω | |

| Differential Input Retour Verloscht | SDDXX | <-12+2* SQRT (f) mat f an GHz | dB | 0,01 ~ 4,1 GHz | ||

| <-6.3+13* Log10 / (f / 5,5) mat f an GHz | dB | 4,1 ~ 11,1 GHz | ||||

| Gemeinsam Modus Ausgang Retour Verloscht | SCCXX | < -7+1,6*f mat f an GHz | dB | 0,01 ~ 2,5 GHz | ||

| -3 | dB | 2,5 ~ 11,1 GHz | ||||

| Ënnerscheed Waveform Verzerrung Eelefmeter | dWDPc | 6,75 | dB | |||

| VMA Verloscht | L | 4.4 | dB | |||

| VMA Verloscht zu Crosstalk Verhältnis | VCR | 32,5 | dB | |||

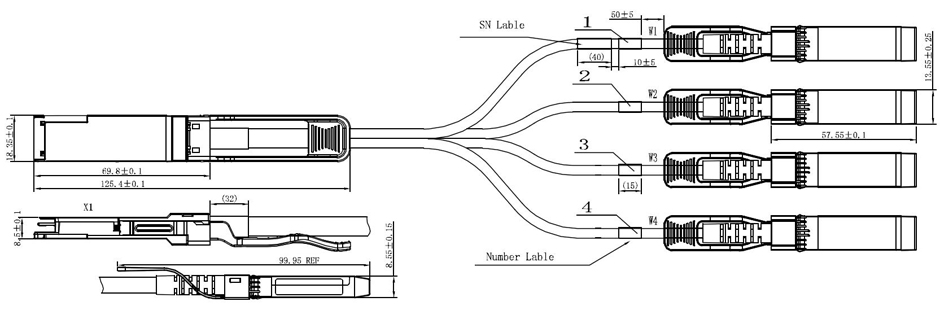

Mechanesch Spezifikatioune

De Stecker ass kompatibel mat der SFF-8436 bis SFF-8432 Spezifizéierung.

| Längt (m) | kann AWG |

| 1 | 30 |

| 3 | 30 |

| 5 | 26 |

| 7 | 26 |

Regulatioun Konformitéit

| Fonktioun | Test Method | Leeschtung |

| Elektrostatesch Entladung (ESD) an den elektresche Pins | MIL-STD-883C Method 3015.7 | Klasse 1 (>2000 Volt) |

| Elektromagnetesch Interferenz (EMI) | FCC Klass B | Konform mat Normen |

| CENELEC EN55022 Class B | ||

| CISPR22 ITE Class B | ||

| RF Immunitéit (RFI) | IEC 61000-4-3 | Weist normalerweis keen moossbare Effekt vun engem 10V/m Feld geschweest vun 80 bis 1000MHz |

| RoHS Konformitéit | RoHS-Direktiv 2011/65/EU an d'Amendement Direktiven 6/6 | RoHS 6/6 konform |