40Gb/s QSFP+ ER4, 40km 1310nm SFP Transceiver JHA-QC40

Eegeschaften:

◊ 4 CWDM Bunnen MUX/DEMUX Design

◊ Bis zu 11.2Gbps pro Kanal Bandbreedung

◊ Aggregat Bandbreed vun> 40Gbps

◊ Duplex LC Connector

◊ Kompatibel mat 40G Ethernet IEEE802.3ba an 40GBASE-ER4 Standard

◊ QSFP MSA kompatibel

◊ APD Fotodetektor

◊ Bis zu 40 km Iwwerdroung

◊ Kompatibel mat QDR / DDR Infiniband Datenraten

◊ Single + 3.3V Energieversuergung Betribssystemer

◊ Built-in digital Diagnostice Funktiounen

◊ Temperaturbereich 0°C bis 70°C

◊ RoHS kompatibel Deel

Uwendungen:

◊ Rack zu Rack

◊ Datenzenter Schalter a Router

◊ Metro Netzwierker

◊ Schalter a Router

◊ 40G BASE-ER4 Ethernet Links

Beschreiwung:

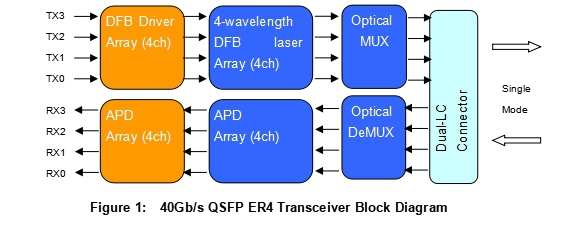

De JHA-QC40 ass e Transceiver Modul entworf fir 40km optesch Kommunikatioun Uwendungen.Den Design entsprécht 40GBASE-ER4 vum IEEE P802.3ba Standard.De Modul konvertéiert 4 Input Channels (ch) vun 10Gb / s elektresch Daten op 4 CWDM optesch Signaler, a multiplexéiert se an een eenzege Kanal fir 40Gb / s optesch Iwwerdroung.Ëmgekéiert, op der Empfänger Säit, de-multiplexéiert de Modul optesch e 40Gb / s Input an 4 CWDM Channels Signaler, a konvertéiert se op 4 Kanal Output elektresch Daten.

Déi zentral Wellelängte vun de 4 CWDM Kanäl sinn 1271, 1291, 1311 an 1331 nm als Membere vum CWDM Wellelängtnetz definéiert am ITU-T G694.2.Et enthält en Duplex LC Connector fir den opteschen Interface an en 38-Pin Connector fir den elektresche Interface.Fir d'optesch Dispersioun am Laangstrecksystem ze minimiséieren, muss Single-Modus Faser (SMF) an dësem Modul applizéiert ginn.

D'Produkt ass entwéckelt mat Formfaktor, opteschen / elektresche Verbindung an digitaler diagnostescher Interface no dem QSFP Multi-Source Agreement (MSA).Et ass entworf fir déi härteste externe Betribsbedéngungen ze treffen, dorënner Temperatur, Fiichtegkeet an EMI Interferenz.

De Modul funktionnéiert vun enger eenzeger +3.3V Energieversuergung an LVCMOS / LVTTL global Kontrollsignaler wéi Modul Present, Reset, Interrupt a Low Power Mode si mat de Moduler verfügbar.Eng 2-Drot Serien Interface ass verfügbar fir méi komplex Kontrollsignaler ze schécken an ze kréien an digital Diagnosinformatioun ze kréien.Eenzel Kanäl kënnen adresséiert ginn an onbenotzt Kanäl kënne fir maximal Designflexibilitéit zougemaach ginn.

De JHA-QC40 ass entworf mat Formfaktor, opteschen / elektresche Verbindung an digitaler diagnostescher Interface no dem QSFP Multi-Source Agreement (MSA).Et ass entworf fir déi härteste externe Betribsbedéngungen ze treffen, dorënner Temperatur, Fiichtegkeet an EMI Interferenz.De Modul bitt ganz héich Funktionalitéit a Feature Integratioun, zougänglech iwwer eng Zwee-Drot Serien Interface.

•Absolut maximal Bewäertungen

| Parameter | Symbol | Min. | Typesch | Max. | Eenheet |

| Späichertemperatur | TS | -40 |

| +85 | °C |

| Versuergung Volt | VCCT, R | -0,5 |

| 4 | V |

| Relativ Fiichtegkeet | RH | 0 |

| 85 | % |

•RecommandéiertOperatioun Ëmfeld:

| Parameter | Symbol | Min. | Typesch | Max. | Eenheet |

| Fall Betribssystemer Temperatur | TC | 0 |

| +70 | °C |

| Versuergung Volt | VCCT, R | +3.13 | 3.3 | +3,47 | V |

| Versuergung aktuell | ICC |

|

| 1000 | mA |

| Power Dissipatioun | PD |

|

| 3.5 | W |

•Elektresch Charakteristiken(TOP = 0 bis 70 °C, VCC = 3,13 bis 3,47 Volt

| Parameter | Symbol | Min | Typ | Max | Eenheet | Note |

| Daten Taux pro Kanal |

| - | 10.3125 | 11.2 | Gbps |

|

| Stroumverbrauch |

| - | 2.5 | 3.5 | W |

|

| Versuergung aktuell | Icc |

| 0,75 | 1.0 | A |

|

| Kontroll ech / O Volt-High | VIH | 2.0 |

| Vcc | V |

|

| Kontroll ech / O Volt-Low | VIL | 0 |

| 0.7 | V |

|

| Inter-Channel Skew | TSK |

|

| 150 | Ps |

|

| RESETL Dauer |

|

| 10 |

| Us |

|

| RESETL De-assert Zäit |

|

|

| 100 | ms |

|

| Power On Zäit |

|

|

| 100 | ms |

|

| Sender | ||||||

| Single Ended Output Volt Toleranz |

| 0.3 |

| 4 | V | 1 |

| Gemeinsam Modus Volt Toleranz |

| 15 |

|

| mV |

|

| Iwwerdroung Input Diff Volt | VI | 150 |

| 1200 | mV |

|

| Iwwerdroung Input Diff Impedanz | ZIN | 85 | 100 | 115 |

|

|

| Donnéeën ofhängeg Input Jitter | DDJ |

| 0.3 |

| UI |

|

| Empfänger | ||||||

| Single Ended Output Volt Toleranz |

| 0.3 |

| 4 | V |

|

| Rx Output Diff Volt | Vo | 370 | 600 | 950 | mV |

|

| Rx Output Rise a Fall Volt | Tr/Tf |

|

| 35 | ps | 1 |

| Total Jitter | TJ |

| 0.3 |

| UI |

|

Notiz:

- 20~80%

•Optesch Parameteren (TOP = 0 bis 70°C, VCC = 3,0 bis 3,6 Volt)

| Parameter | Symbol | Min | Typ | Max | Eenheet | Ref. |

| Sender | ||||||

| Wellelängt Aufgab | L0 | 1264,5 | 1271 | 1277,5 | nm |

|

| L1 | 1284,5 | 1291 | 1297,5 | nm |

| |

| L2 | 1304,5 | 1311 | 1317,5 | nm |

| |

| L3 | 1324,5 | 1331 | 1337,5 | nm |

| |

| Side-Modus Ënnerdréckungsverhältnis | SMSR | 30 | - | - | dB |

|

| Total Moyenne Start Muecht | PT | - | - | 8.3 | dBm |

|

| Duerchschnëtt Start Power, all Lane |

| -3 | - | 5 | dBm |

|

| TDP, all Lane | TDP |

|

| 2.3 | dB |

|

| Ausstierwen Verhältnis | ER | 3.5 | 6.0 |

| dB | |

| Sender Eye Mask Definitioun {X1, X2, X3, Y1, Y2, Y3} |

| {0.25, 0.4, 0.45, 0.25, 0.28, 0.4} |

| |||

| Optesch Retour Verloscht Toleranz |

| - | - | 20 | dB |

|

| Duerchschnëtt Start Power OFF Sender, all Lane | Poff |

|

| -30 | dBm |

|

| Relativ Intensitéit Kaméidi | Rin |

|

| -128 | dB/HZ | 1 |

| Optesch Retour Verloscht Toleranz |

| - | - | 12 | dB |

|

| Empfänger | ||||||

| Schued Schwell | THd | 3 |

|

| dBm | 1 |

| Duerchschnëtt Kraaft um Empfängerinput, all Lane | R | -21 |

| -6 | dBm |

|

| Kritt elektresch 3 dB iewescht Ausschneiden Frequenz, all Lane |

|

|

| 12.3 | GHz |

|

| RSSI Genauegkeet |

| -2 |

| 2 | dB |

|

| Empfänger Reflexioun | Rrx |

|

| -26 | dB |

|

| Receiver Power (OMA), all Lane |

| - | - | 3.5 | dBm |

|

| Kréien elektresch 3 dB ieweschte Cutoff Frequenz, all Lane |

|

|

| 12.3 | GHz |

|

| LOS De-Assert | LOSD |

|

| -25 | dBm |

|

| LOS Assert | LOSA | -35 |

|

| dBm |

|

| LOS Hysteresis | LOSH | 0,5 |

|

| dB |

|

Note

- 12dB Reflexioun

•Diagnostic Iwwerwachung Interface

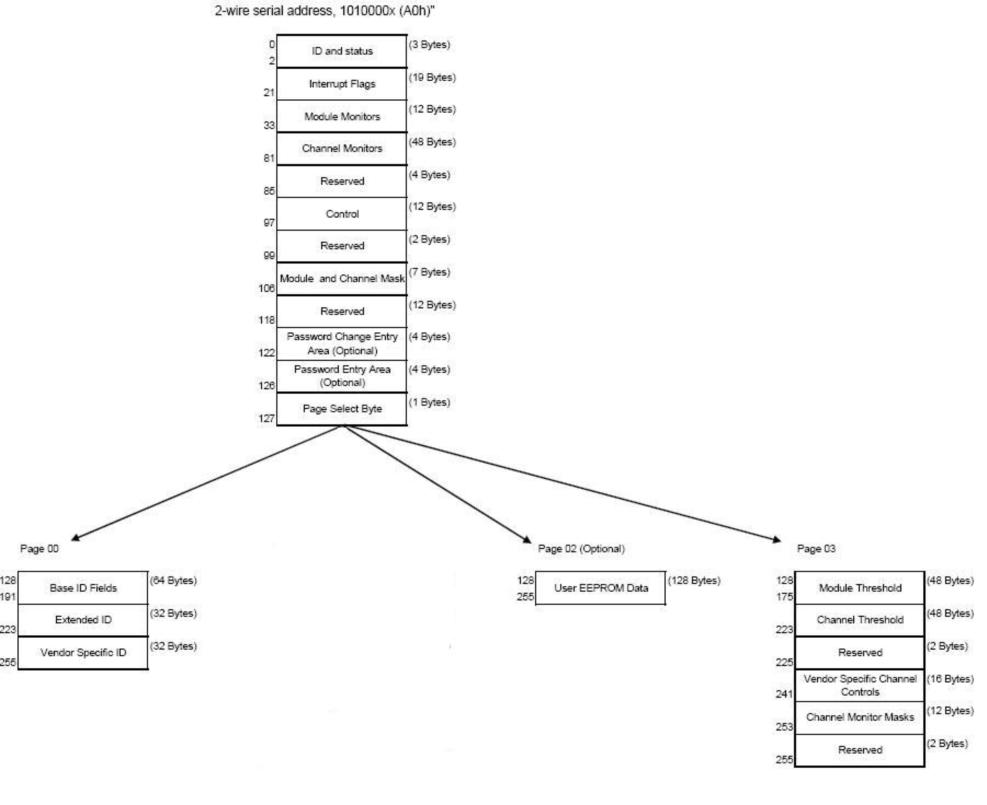

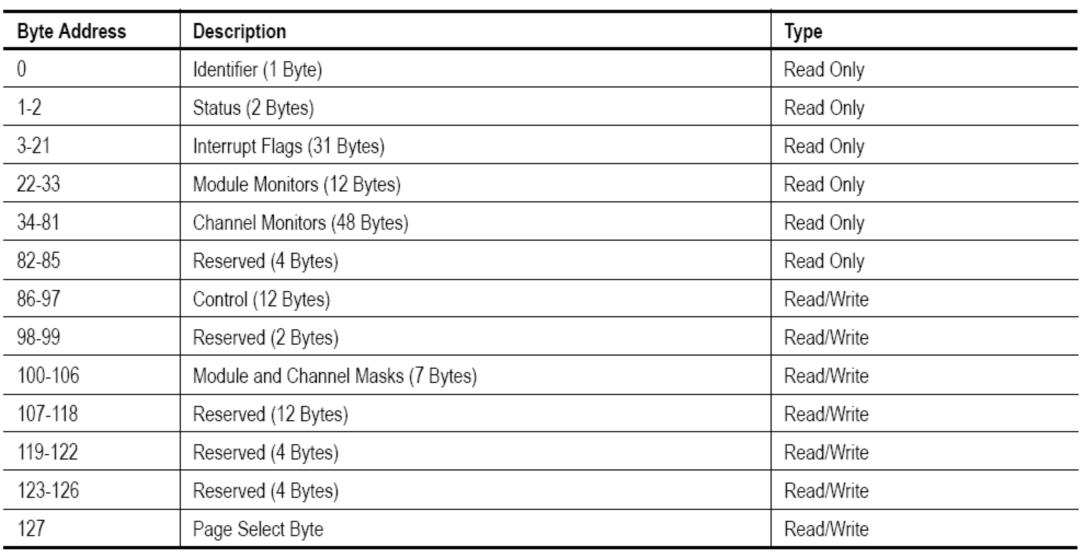

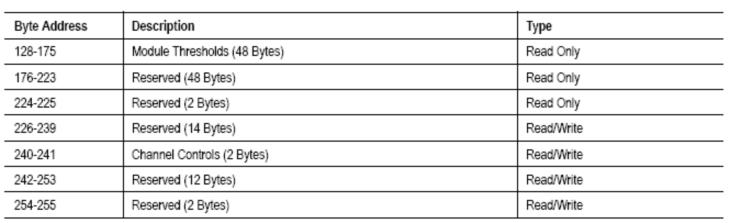

Digital Diagnostik Iwwerwaachungsfunktioun ass op all QSFP+ ER4 verfügbar.A 2-Drot Serien Interface gëtt Benotzer Kontakt mat Modul.D'Struktur vun der Erënnerung gëtt a fléissend gewisen.De Gedächtnisraum ass arrangéiert an eng ënnescht, eenzeg Säit, Adressraum vun 128 Bytes a méi iewescht Adressraum Säiten.Dës Struktur erlaabt fristgerecht Zougang zu Adressen op der ënneschter Säit, sou wéi Interrupt Flags a Monitore.Manner Zäit kritesch Zäit Entréen, wéi Serien ID Informatiounen a Schwellen Astellungen, sinn mat der Page Select Funktioun verfügbar.D'Interface Adress benotzt ass A0xh a gëtt haaptsächlech fir Zäitkritesch Daten wéi Ënnerbriechungshandhabung benotzt fir eng eemoleg Liesung fir all Daten am Zesummenhang mat enger Ënnerbriechungssituatioun z'erméiglechen.No engem Ënnerbriechung, IntL ass behaapt ginn, kann de Host de Fändelfeld ausliesen fir de betraffene Kanal an den Typ vu Fändel ze bestëmmen.

EEPROM Serial ID Memory Inhalt (A0h)

| Daten Adress | Längt | Numm vun Längt | Beschreiwung an Inhalter | |

| Basis ID Felder | ||||

| 128 | 1 | Identifizéierer | Identifizéierer Typ vum Serien Modul (D=QSFP+) | |

| 129 | 1 | Ext.Identifizéierer | Erweidert Identifizéierer vum Serial Modul (90 = 2.5W) | |

| 130 | 1 | Connector | Code vum Connector Typ (7 = LC) | |

| 131-138 | 8 | Spezifizéierung Konformitéit | Code fir elektronesch Kompatibilitéit oder optesch Kompatibilitéit (40GBASE-LR4) | |

| 139 | 1 | Kodéierung | Code fir Serien Kodéierung Algorithmus (5 = 64B66B) | |

| 140 | 1 | BR, nominal | Nominell Bitrate, Eenheeten vun 100 MBits/s (6C=108) | |

| 141 | 1 | Verlängert Tarif wielt Compliance | Tags fir erweidert Taux wielt Konformitéit | |

| 142 | 1 | Längt (SMF) | Link Längt ënnerstëtzt fir SMF Faser a km (28=40KM) | |

| 143 | 1 | Längt (OM3 50um) | Link Längt ënnerstëtzt fir EBW 50/125um Faser (OM3), Eenheeten vun 2m | |

| 144 | 1 | Längt (OM2 50um) | Link Längt ënnerstëtzt fir 50/125um Faser (OM2), Eenheeten vun 1m | |

| 145 | 1 | Längt (OM1 62.5um) | Link Längt ënnerstëtzt fir 62,5 / 125um Faser (OM1), Unitéiten vun 1m | |

| 146 | 1 | Längt (Kupfer) | Linklängt vu Kupfer oder aktive Kabel, Eenheeten vun 1m Linklängt ënnerstëtzt fir 50/125um Faser (OM4), Eenheeten vun 2m wann Byte 147 850nm VCSEL deklaréiert wéi an Table 37 definéiert | |

| 147 | 1 | Apparat Tech | Apparat Technologie | |

| 148-163 | 16 | Verkeefer Numm | QSFP+ Verkeefer Numm: TIBTRONIX (ASCII) | |

| 164 | 1 | Verlängert Modul | Verlängert Modul Coden fir InfiniBand | |

| 165-167 | 3 | Verkeefer OUI | QSFP+ Verkeefer IEEE Firma ID (000840) | |

| 168-183 | 16 | Verkeefer PN | Artikelnummer: JHA-QC40 (ASCII) | |

| 184-185 | 2 | Verkeefer rev | Revisiounsniveau fir Deelnummer geliwwert vum Verkeefer (ASCII) (X1) | |

| 186-187 | 2 | Wellelängt oder Kupferkabel Dämpfung | Nominell Laserwellelängt (Wellelängt = Wäert / 20 an nm) oder Kupferkabel Dämpfung an dB bei 2,5 GHz (Adrs 186) an 5,0 GHz (Adrs 187) (65A4 = 1301) | |

| 188-189 | 2 | Wellelängt Toleranz | Garantéiert Gamme vu Laser Wellelängt (+/- Wäert) aus nominal Wellelängt.(Wellelängt Tol.=Wäert/200 an nm) (1C84=36.5) | |

| 190 | 1 | Max Fall Temperatur. | Maxinum Këschttemperatur an Grad C (70) | |

| 191 | 1 | CC_BASE | Check Code fir Basis ID Felder (Adressen 128-190) | |

| Verlängert ID Felder | ||||

| 192-195 | 4 | Optiounen | Rate Select, TX Disable, Tx Fault, LOS, Warnindikatoren fir: Temperatur, VCC, RX, Power, TX Bias | |

| 196-211 | 16 | Verkeefer SN | Serienummer geliwwert vum Verkeefer (ASCII) | |

| 212-219 | 8 | Datum Code | Hiersteller Datum Code vum Verkeefer | |

| 220 | 1 | Diagnostic Iwwerwachung Typ | Gëtt un wéi eng Zorte vu diagnostescher Iwwerwaachung (wann iwwerhaapt) am Modul ëmgesat ginn.Bit 1, 0 Reservéiert (8=Moyenne Power) | |

| 221 | 1 | Erweidert Optiounen | Gëtt un wéi eng optional verbessert Features am Modul implementéiert sinn. | |

| 222 | 1 | Reservéiert | ||

| 223 | 1 | CC_EXT | Check Code fir déi erweidert ID Felder (Adressen 192-222) | |

| Verkeefer spezifesch ID Felder | ||||

| 224-255 | 32 | Verkeefer spezifesch EEPROM | ||

•Timing fir Soft Kontroll a Status Funktiounen

| Parameter | Symbol | Max | Eenheet | Konditiounen |

| Initialiséierung Zäit | t_init | 2000 | ms | Zäit vu Kraaft on1, Hot Plug oder Rising Rand of Reset bis de Modul voll funktionell ass2 |

| Reset Init Assert Time | t_reset_init | 2 | μs | E Reset gëtt generéiert vun engem nidderegen Niveau méi laang wéi déi minimal Reset-Pulszäit, déi um ResetL Pin ass. |

| Serial Bus Hardware Ready Time | t_seriell | 2000 | ms | Zäit vu Kraaft on1 bis Modul reagéiert op Dateniwwerdroung iwwer den 2-Drot Serien Bus |

| Monitor Data ReadyZäit | t_daten | 2000 | ms | Zäit vum Power on1 bis Daten net fäerdeg, Bit 0 vum Byte 2, deassertéiert an IntL behaapt |

| Reset Assert Time | t_reset | 2000 | ms | Zäit vum Rising Rand um ResetL Pin bis de Modul voll funktionell ass2 |

| LPMode Assert Zäit | ton_LPMode | 100 | μs | Zäit vun der Behaaptung vum LPMode (Vin:LPMode =Vih) bis de Modul Kraaftverbrauch e méi nidderegen Power Level erakënnt |

| IntL Assert Zäit | ton_IntL | 200 | ms | Zäit vun der Optriede vun der Konditioun déi IntL ausléist bis Vout:IntL = Vol |

| IntL Deassert Zäit | toff_IntL | 500 | μs | toff_IntL 500 μs Zäit vun kloer op read3 Operatioun vun assoziéiert Fändel bis Vout: IntL = Voh.Dëst beinhalt deassert mol fir Rx LOS, Tx Fault an aner Fändel Bits. |

| Rx LOS behaapt Zäit | tonn_los | 100 | ms | Zäit vun Rx LOS Staat ze Rx LOS bëssen gesat an IntL behaapt |

| Fändel Assert Time | tonn_flag | 200 | ms | Zäit vun Optriede vun Konditioun Fändel ausléisen zu assoziéiert Fändel Bit Set an IntL behaapt |

| Mask behaapten Zäit | ton_mask | 100 | ms | Zäit vum Mask Bit set4 bis assoziéiert IntL Behaaptung verhënnert gëtt |

| Mask De-assert Zäit | toff_mask | 100 | ms | Zäit vun der Mask bit geläscht4 bis verbonne IntlL Operatioun erëm |

| ModSelL Assert Zäit | ton_ModSelL | 100 | μs | Zäit vun Behaaptung vun ModSelL bis Modul reagéiert op Daten Transmissioun iwwer den 2-Drot Serien Bus |

| ModSelL Deassert Zäit | toff_ModSelL | 100 | μs | Zäit vun der Deassertioun vum ModSelL bis de Modul net op d'Dateniwwerdroung iwwer den 2-Drot Serienbus reagéiert |

| Power_over-ride oderPower-set Assert Time | tonn_Pdown | 100 | ms | Zäit aus P_Down bëssen gesat 4 bis Modul Stroumconsommatioun an ënneschten Power Level |

| Power_over-ride oder Power-set De-assert Time | toff_Pdown | 300 | ms | Zäit vum P_Down bëssen geläscht4 bis de Modul voll funktionell3 |

Note:

1. Power on ass definéiert wéi de Moment wou d'Versuergungsspannungen op oder iwwer dem Minimum spezifizéierte Wäert erreechen a bleiwen.

2. Ganz funktionell definéiert als IntL behaapt wéinst Daten net prett bëssen, bëssen 0 Byte 2 de-behaapt.

3. Mooss vun falen Auer Rand no stoppen bëssen vun liesen Transaktioun.

4. Mooss vun falen Auer Rand no stoppen bëssen vun schreiwen Transaktioun.

•Transceiver Block Diagram

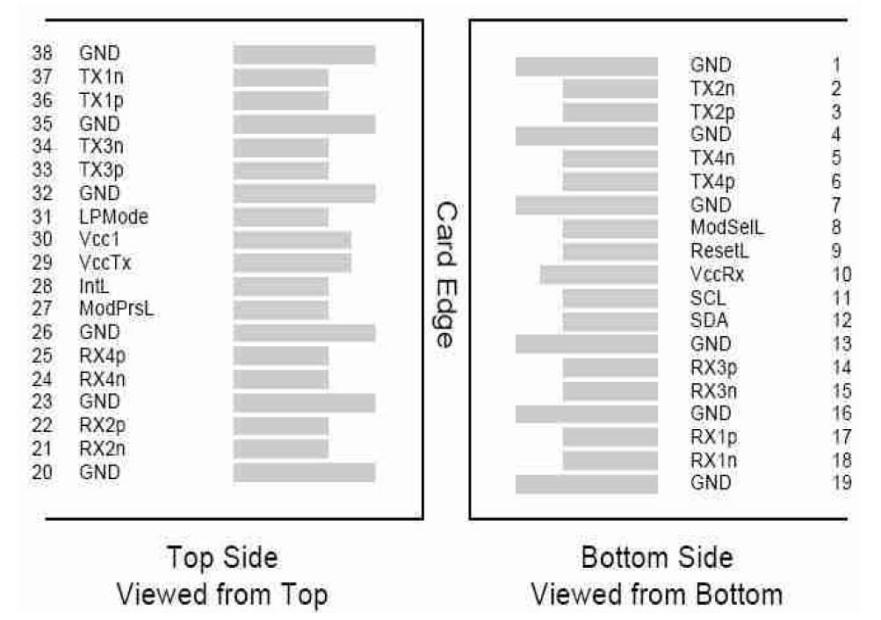

•Pin Assignment

Diagramm vum Host Board Connector Block Pin Nummeren an Numm

•PinBeschreiwung

| Pin | Logik | Symbol | Numm / Beschreiwung | Ref. |

| 1 |

| GND | Buedem | 1 |

| 2 | CML-I | tx2n | Sender Inverted Data Input |

|

| 3 | CML-I | tx2p | Sender Non-Inverted Data Output |

|

| 4 |

| GND | Buedem | 1 |

| 5 | CML-I | tx4n | Sender Inverted Data Output |

|

| 6 | CML-I | tx4p | Sender Non-Inverted Data Output |

|

| 7 |

| GND | Buedem | 1 |

| 8 | LVTTL-I | ModSel | Modul Wielt |

|

| 9 | LVTTL-I | Reset L | Modul zréckgesat |

|

| 10 |

| VccRx | +3.3V Power Supply Receiver | 2 |

| 11 | LVCMOS-I/O | SCL | 2-Drot Serial Interface Auer |

|

| 12 | LVCMOS-I/O | SDA | 2-Drot Serial Interface Daten |

|

| 13 |

| GND | Buedem | 1 |

| 14 | CML-O | rx3p | Empfänger Inverted Data Output |

|

| 15 | CML-O | rx3 n | Receiver Non-Inverted Data Output |

|

| 16 |

| GND | Buedem | 1 |

| 17 | CML-O | rx1p | Empfänger Inverted Data Output |

|

| 18 | CML-O | rx1n | Receiver Non-Inverted Data Output |

|

| 19 |

| GND | Buedem | 1 |

| 20 |

| GND | Buedem | 1 |

| 21 | CML-O | rx2n | Empfänger Inverted Data Output |

|

| 22 | CML-O | rx2p | Receiver Non-Inverted Data Output |

|

| 23 |

| GND | Buedem | 1 |

| 24 | CML-O | rx4n | Empfänger Inverted Data Output |

|

| 25 | CML-O | rx4p | Receiver Non-Inverted Data Output |

|

| 26 |

| GND | Buedem | 1 |

| 27 | LVTTL-O | ModPrsL | Modul Present |

|

| 28 | LVTTL-O | IntL | Ënnerbriechung |

|

| 29 |

| VccTx | +3.3V Stromforsyning Sender | 2 |

| 30 |

| vcc1 | +3.3V Stroumversuergung | 2 |

| 31 | LVTTL-I | LPMode | Low Power Modus |

|

| 32 |

| GND | Buedem | 1 |

| 33 | CML-I | tx3p | Sender Inverted Data Output |

|

| 34 | CML-I | tx3n | Sender Non-Inverted Data Output |

|

| 35 |

| GND | Buedem | 1 |

| 36 | CML-I | tx 1p | Sender Inverted Data Output |

|

| 37 | CML-I | tx1n | Sender Non-Inverted Data Output |

|

| 38 |

| GND | Buedem | 1 |

Notizen:

- GND ass d'Symbol fir eenzel a Versuergung (Kraaft) gemeinsam fir QSFP Moduler, All si gemeinsam am QSFP Modul an all Modulspannungen ginn op dëst Potenzial referenzéiert soss bemierkt.Connect dës direkt un der Gaascht Verwaltungsrot Signal gemeinsam Buedem Fliger.Laser Output behënnert op TDIS> 2.0V oder oppen, aktivéiert op TDIS <0.8V.

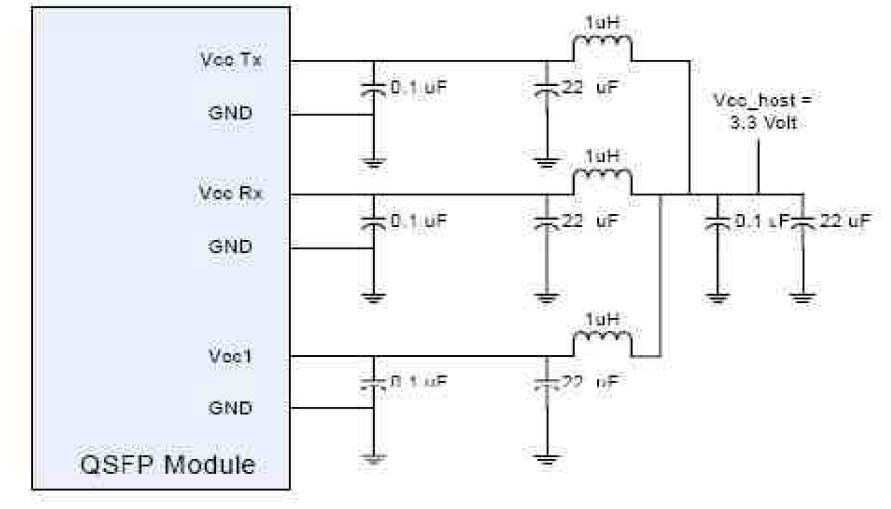

- VccRx, Vcc1 a VccTx sinn den Empfänger a Sender Kraaft Fournisseuren a solle gläichzäiteg applizéiert ginn.Recommandéiert Hostboard Stroumversuergungsfilter gëtt hei ënnen gewisen.VccRx, Vcc1 a VccTx kënnen intern am QSFP Transceiver Modul an all Kombinatioun verbonne sinn.D'Connector Pins sinn all bewäert fir maximal Stroum vu 500mA.

•Recommandéiert Circuit

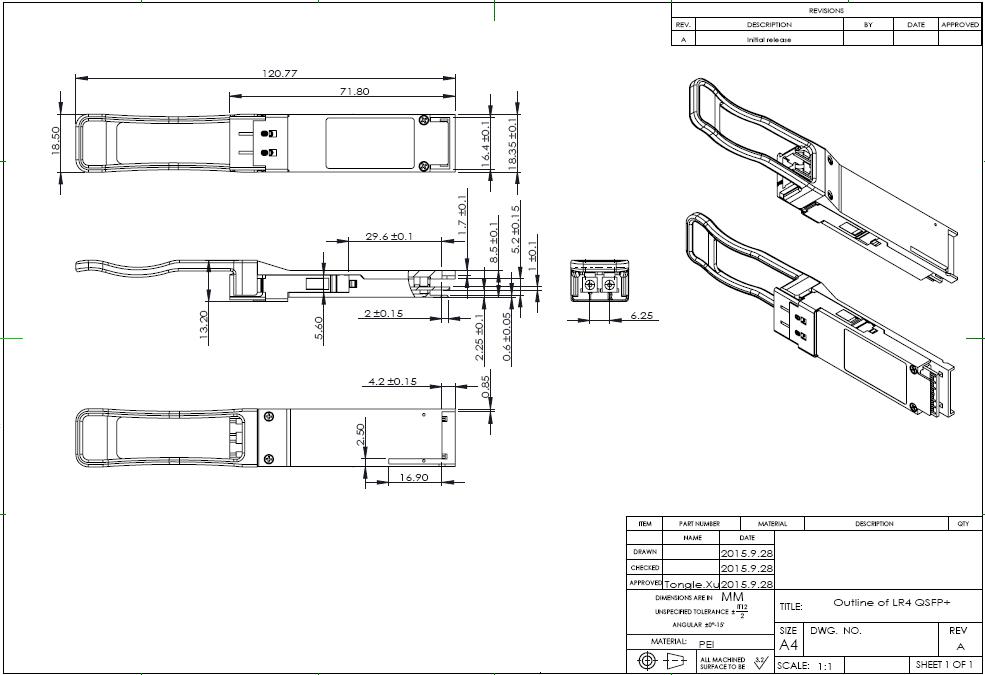

•Mechanesch Dimensiounen