100 Gb/S QSFP28 1310 nm 10 km LR4 LC-Transceiver JHAQ28C10C

Merkmale:

◊ 4-spuriges MUX/DEMUX-Design

◊ Integriertes CWDM TOSA/ROSA für bis zu 10 km Reichweite über SMF

◊ Unterstützt 100GBASE-CWDM4 für eine Leitungsrate von 103,125 Gbit/s und OTU4 für eine Leitungsrate von 111,81 Gbit/s

◊ Gesamtbandbreite von > 100 Gbit/s

◊ Duplex-LC-Anschlüsse

◊ Konform mit dem Standard IEEE 802.3-2012 Klausel 88 IEEE 802.3bm CAUI-4-Chip-zu-Modul-Elektrostandard ITU-T G.959.1-2012-02-Standard ·

◊ Einzelnes +3,3-V-Netzteil in Betrieb

◊ Integrierte digitale Diagnosefunktionen

◊ Temperaturbereich 0°C bis 70°C

◊ RoHS-konformes Teil

Anwendungen:

◊ Lokales Netzwerk (LAN)

◊ Wide Area Network (WAN)

◊ Ethernet-Switches und Router-Anwendungen

Beschreibung:

Das JHAQ28C10C ist ein Transceiver-Modul, das für optische Kommunikationsanwendungen im Umkreis von 10 km entwickelt wurde.Das Design entspricht 100GbASE-LR4 des Standards IEEE 802.3-2012 Klausel 88, IEEE 802.3bm CAUI-4-Chip-zu-Modul-Elektrostandard ITU-T G.959.1-2012-02.Das Modul wandelt 4 Eingangskanäle (Kanäle) mit 25,78 Gbit/s bis 27,95 Gbit/s elektrische Daten in 4-spurige optische Signale um und multiplext sie in einen einzigen Kanal für eine optische 100-Gbit/s-Übertragung.Umgekehrt demultiplext das Modul auf der Empfängerseite einen 100-Gbit/s-Eingang optisch in 4-spurige Signale und wandelt sie in elektrische Ausgangsdaten mit 4-spurigen Ausgängen um.

Die zentralen Wellenlängen der 4 Bahnen betragen 1270 nm, 1290 nm, 1310 nm und 1330 nm.Es enthält einen Duplex-LC-Stecker für die optische Schnittstelle und einen 38-poligen Stecker für die elektrische Schnittstelle.Um die optische Dispersion im Langstreckensystem zu minimieren, muss in diesem Modul Singlemode-Faser (SMF) eingesetzt werden.

Das Produkt ist mit Formfaktor, optischer/elektrischer Verbindung und digitaler Diagnoseschnittstelle gemäß dem QSFP28 Multi-Source Agreement (MSA) konzipiert.Es wurde entwickelt, um den härtesten externen Betriebsbedingungen gerecht zu werden, einschließlich Temperatur, Feuchtigkeit und EMI-Störungen.

Das Modul wird mit einer einzigen +3,3-V-Stromversorgung betrieben und die Module verfügen über globale LVCMOS/LVTTL-Steuersignale wie „Module Present“, „Reset“, „Interrupt“ und „Low Power Mode“.Zum Senden und Empfangen komplexerer Steuersignale sowie zum Erhalten digitaler Diagnoseinformationen steht eine serielle 2-Draht-Schnittstelle zur Verfügung.Für maximale Designflexibilität können einzelne Kanäle adressiert und ungenutzte Kanäle abgeschaltet werden.

Der JHAQ28C10C ist mit Formfaktor, optischer/elektrischer Verbindung und digitaler Diagnoseschnittstelle gemäß dem QSFP28 Multi-Source Agreement (MSA) konzipiert.Es wurde entwickelt, um den härtesten externen Betriebsbedingungen gerecht zu werden, einschließlich Temperatur, Feuchtigkeit und EMI-Störungen.Das Modul bietet eine sehr hohe Funktionalität und Funktionsintegration, zugänglich über eine zweiadrige serielle Schnittstelle.

•absolut beste Bewertungen

| Parameter | Symbol | Mindest. | Typisch | Max. | Einheit |

| Lagertemperatur | TS | -40 |

| +85 | °C |

| Versorgungsspannung | VCCT, R | -0,5 |

| 4 | V |

| Relative Luftfeuchtigkeit | RH | 0 |

| 85 | % |

•EmpfohlenBetriebsumgebung:

| Parameter | Symbol | Mindest. | Typisch | Max. | Einheit |

| Gehäusebetriebstemperatur | TC | 0 |

| +70 | °C |

| Versorgungsspannung | VCCT, R | +3.13 | 3.3 | +3,47 | V |

| Versorgungsstrom | ICC |

| 1100 | 1500 | mA |

| Energieverschwendung | PD |

|

| 5 | W |

•Elektrische Eigenschaften(TOP = 0 bis 70 °C, VCC = 3,13 bis 3,47 Volt

| Parameter | Symbol | Mindest | Typ | Max | Einheit | Notiz | ||

| Datenrate pro Kanal |

| - | 25.78125 |

| Gbit/s |

| ||

|

|

| 27.9525 |

|

| ||||

| Energieverbrauch |

| - | 2.7 | 3.5 | W |

| ||

| Versorgungsstrom | Icc |

| 0,8 | 1 | A |

| ||

| Steuer-E/A-Spannung hoch | VIH | 2,0 |

| Vcc | V |

| ||

| Steuer-E/A-Spannung niedrig | VIL | 0 |

| 0,7 | V |

| ||

| Inter-Channel-Skew | TSK |

|

| 35 | Ps |

| ||

| RESETL-Dauer |

|

| 10 |

| Us |

| ||

| RESETL Deaktivierungszeit |

|

|

| 100 | ms |

| ||

| Einschaltzeit |

|

|

| 100 | ms |

| ||

| Sender | ||||||||

| Single-Ended-Ausgangsspannungstoleranz |

| 0,3 |

| Vcc | V | 1 | ||

| Gleichtaktspannungstoleranz |

| 15 |

|

| mV |

| ||

| Eingangsdifferenzspannung übertragen | VI | 150 |

| 1200 | mV |

| ||

| Differenzimpedanz des Sendeeingangs | ZIN | 85 | 100 | 115 |

|

| ||

| Datenabhängiger Eingabe-Jitter | DDJ |

| 0,3 |

| UI |

| ||

| Empfänger | ||||||||

| Single-Ended-Ausgangsspannungstoleranz |

| 0,3 |

| 4 | V |

| ||

| Rx-Ausgangsdifferenzspannung | Vo | 370 | 600 | 950 | mV |

| ||

| Anstiegs- und Abfallspannung des Rx-Ausgangs | Tr/Tf |

|

| 35 | ps | 1 | ||

| Totaler Jitter | TJ |

| 0,3 |

| UI |

| ||

Notiz:

- 20~80 %

•Optische Parameter (TOP = 0 bis 70°C, VCC = 3,0 bis 3,6 Volt)

| Parameter | Symbol | Mindest | Typ | Max | Einheit | Ref. | ||

| Sender | ||||||||

| Wellenlängenzuordnung | L0 | 1264,5 | 1271 | 1277,5 | nm |

| ||

| L1 | 1284,5 | 1291 | 1297,5 | nm |

| |||

| L2 | 1304.5 | 1311 | 1317,5 | nm |

| |||

| L3 | 1324,5 | 1331 | 1337,5 | nm |

| |||

| Nebenmodus-Unterdrückungsverhältnis | SMSR | 30 | - | - | dB |

| ||

| Gesamte durchschnittliche Startleistung | PT | -6 | - | 6.5 | dBm |

| ||

| Durchschnittliche Startleistung, jede Spur |

| -6 | - | 2.5 | dBm |

| ||

| Unterschied in der Startleistung zwischen zwei beliebigen Bahnen (OMA) |

| - | - | 3.5 | dB |

| ||

| TDP, jede Spur | TDP |

|

| 2.2 | dB |

| ||

| Aussterbeverhältnis | ER | 4 | - | - | dB | |||

| Definition der Sender-Augenmaske {X1, X2, X3, Y1, Y2, Y3} |

| {0,25, 0,4, 0,45, 0,25, 0,28, 0,4} |

| |||||

| Toleranz der optischen Rückflussdämpfung |

| - | - | 20 | dB |

| ||

| Durchschnittlicher Start-Power-OFF-Sender, jede Spur | Poff |

|

| -30 | dBm |

| ||

| Relatives Intensitätsrauschen | Rin |

|

| -128 | dB/Hz | 1 | ||

| Toleranz der optischen Rückflussdämpfung |

| - | - | 12 | dB |

| ||

| Empfänger | ||||||||

| Schadensschwelle | THd | 3.3 |

|

| dBm | 1 | ||

| Durchschnittliche Leistung am Empfängereingang, jede Spur | R | -13,0 |

| 0 | dBm |

| ||

| RSSI-Genauigkeit |

| -2 |

| 2 | dB |

| ||

| Reflexionsgrad des Empfängers | Rrx |

|

| -26 | dB |

| ||

| Empfängerleistung (OMA), jede Spur |

| - | - | 3.5 | dBm |

| ||

| LOS De-Assert | LOSD |

|

| -15 | dBm |

| ||

| LOS-Bestätigung | LOSA | -25 |

|

| dBm |

| ||

| LOS-Hysterese | LOSH | 0,5 |

|

| dB |

| ||

Notiz

- 12 dB Reflexion

•Schnittstelle zur Diagnoseüberwachung

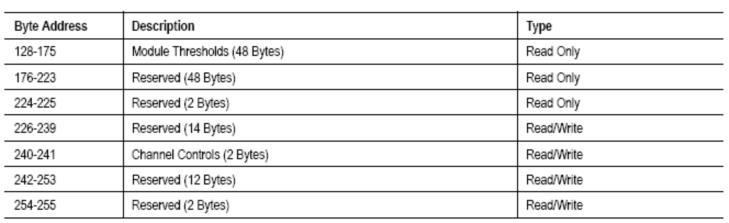

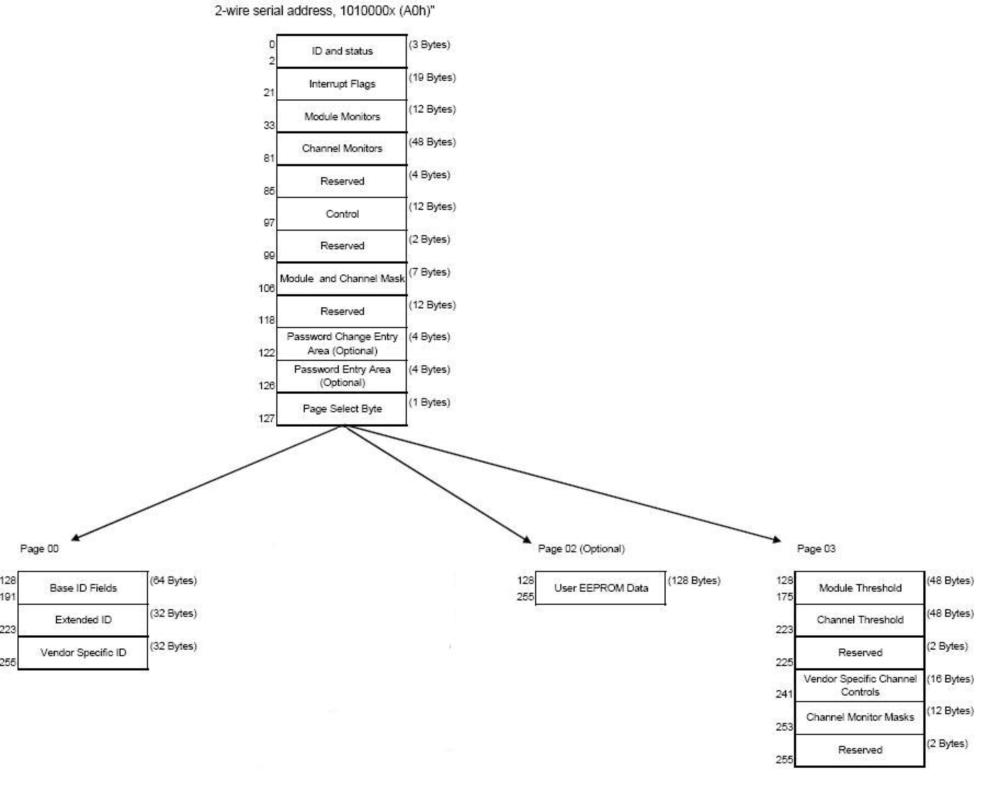

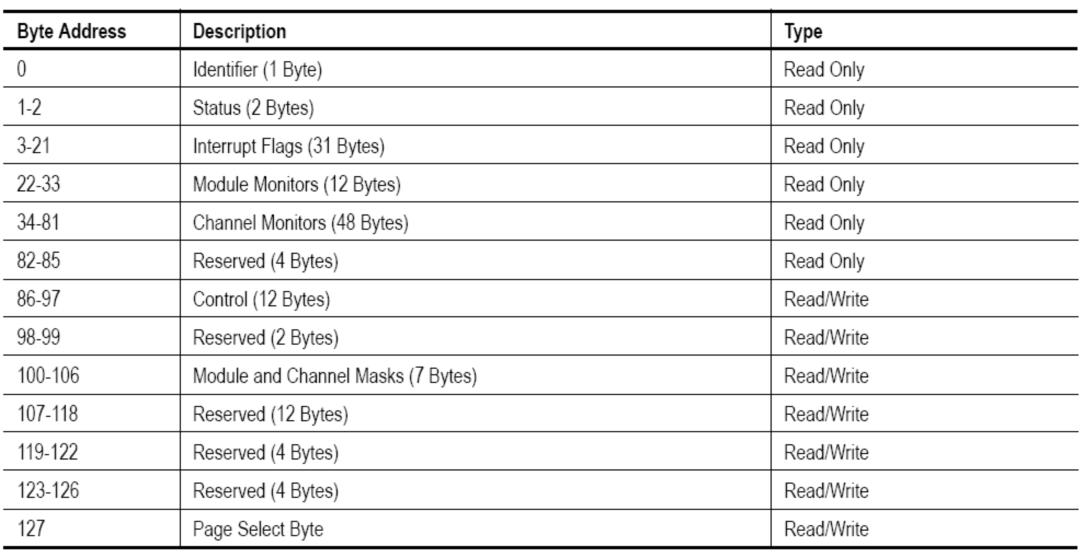

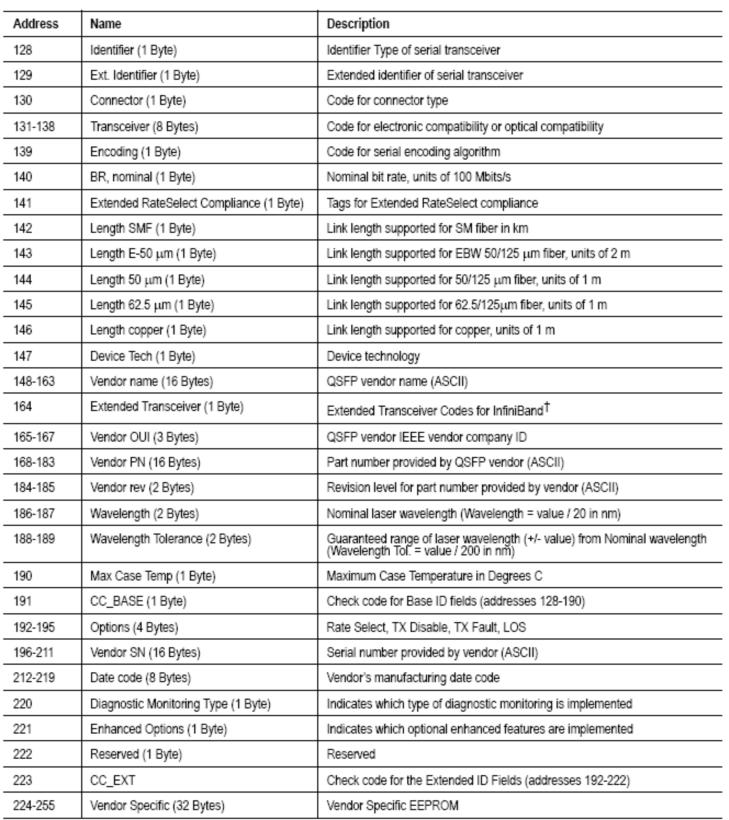

Die digitale Diagnoseüberwachungsfunktion ist auf allen QSFP28 LR4 verfügbar.Eine serielle 2-Draht-Schnittstelle ermöglicht dem Benutzer die Kontaktaufnahme mit dem Modul.Die Struktur des Gedächtnisses wird fließend dargestellt.Der Speicherplatz ist in einen unteren, einseitigen Adressraum von 128 Bytes und mehrere obere Adressraumseiten unterteilt.Diese Struktur ermöglicht den zeitnahen Zugriff auf Adressen auf der unteren Seite, z. B. Interrupt-Flags und Monitore.Weniger zeitkritische Zeiteinträge, wie z. B. Informationen zur Seriennummer und Schwellenwerteinstellungen, sind mit der Funktion „Seitenauswahl“ verfügbar.Die verwendete Schnittstellenadresse ist A0xh und wird hauptsächlich für zeitkritische Daten wie die Interrupt-Verarbeitung verwendet, um ein einmaliges Lesen aller Daten im Zusammenhang mit einer Interrupt-Situation zu ermöglichen.Nachdem ein Interrupt, IntL, aktiviert wurde, kann der Host das Flag-Feld auslesen, um den betroffenen Kanal und den Flag-Typ zu bestimmen.

Seite02 ist das Benutzer-EEPROM und sein Format wird vom Benutzer festgelegt.

Die detaillierte Beschreibung von „Low Memory“ und „Page00.page03 Upper Memory“ finden Sie im SFF-8436-Dokument.

•Timing für Soft-Control- und Statusfunktionen

| Parameter | Symbol | Max | Einheit | Bedingungen |

| Initialisierungszeit | t_init | 2000 | ms | Zeit vom Einschalten1, Hot-Plug oder steigender Reset-Flanke bis zur vollständigen Funktionsfähigkeit des Moduls2 |

| Setzen Sie die Init-Assert-Zeit zurück | t_reset_init | 2 | μs | Ein Reset wird durch einen Low-Pegel erzeugt, der länger als die minimale Reset-Impulszeit am ResetL-Pin liegt. |

| Bereitschaftszeit der seriellen Bus-Hardware | t_serial | 2000 | ms | Zeit vom Einschalten1 bis das Modul auf die Datenübertragung über den seriellen 2-Draht-Bus reagiert |

| Monitordaten bereitZeit | t_data | 2000 | ms | Zeit vom Einschalten1 bis zur Nichtbereitstellung der Daten, Bit 0 von Byte 2, deaktiviert und IntL aktiviert |

| Setzen Sie die Bestätigungszeit zurück | t_reset | 2000 | ms | Zeit von der steigenden Flanke am ResetL-Pin bis zur vollständigen Funktionsfähigkeit des Moduls2 |

| LPMode-Assert-Zeit | ton_LPMode | 100 | μs | Zeit von der Aktivierung des LPMode (Vin:LPMode =Vih), bis der Stromverbrauch des Moduls einen niedrigeren Leistungspegel erreicht |

| IntL-Bestätigungszeit | ton_IntL | 200 | ms | Zeit vom Eintreten der Bedingung, die IntL auslöst, bis Vout:IntL = Vol |

| IntL Deaktivierungszeit | toff_IntL | 500 | μs | toff_IntL 500 μs Zeit vom Löschen des Lese3-Vorgangs des zugehörigen Flags bis Vout:IntL = Voh.Dazu gehören Deaktivierungszeiten für Rx LOS, Tx Fault und andere Flag-Bits. |

| Rx LOS Assert-Zeit | ton_los | 100 | ms | Zeit vom Rx-LOS-Zustand bis zum Setzen des Rx-LOS-Bits und der Bestätigung von IntL |

| Flag-Assert-Zeit | ton_flag | 200 | ms | Zeit vom Auftreten des bedingungsauslösenden Flags bis zum Setzen des zugehörigen Flag-Bits und der Geltendmachung von IntL |

| Mask-Assert-Zeit | ton_mask | 100 | ms | Zeit vom Setzen des Maskenbits4 bis zur Sperrung der zugehörigen IntL-Assertion |

| Mask-Deaktivierungszeit | toff_mask | 100 | ms | Zeit vom Löschen des Maskenbits4 bis zur Wiederaufnahme des zugehörigen IntlL-Vorgangs |

| ModSelL Assert-Zeit | ton_ModSelL | 100 | μs | Zeit von der Aktivierung von ModSelL bis zur Reaktion des Moduls auf die Datenübertragung über den seriellen 2-Draht-Bus |

| ModSelL-Deaktivierungszeit | toff_ModSelL | 100 | μs | Zeit von der Aufhebung von ModSelL bis das Modul nicht mehr auf die Datenübertragung über den seriellen 2-Draht-Bus reagiert |

| Power_over-ride oderPower-Set-Assert-Zeit | ton_Pdown | 100 | ms | Zeit vom Setzen des P_Down-Bits 4 bis zum Erreichen des niedrigeren Leistungsniveaus des Modulstromverbrauchs |

| Power_over-ride oder Power-set De-assert Time | toff_Pdown | 300 | ms | Zeit vom Löschen des P_Down-Bits4 bis zur vollständigen Funktionsfähigkeit des Moduls3 |

Notiz::

1. Einschalten ist definiert als der Moment, in dem die Versorgungsspannungen den angegebenen Mindestwert erreichen und auf diesem oder darüber bleiben.

2. Voll funktionsfähig ist definiert als IntL aktiviert aufgrund des Daten-nicht-bereit-Bits, Bit 0 Byte 2 deaktiviert.

3. Gemessen ab der fallenden Taktflanke nach dem Stoppbit der Lesetransaktion.

4. Gemessen ab der fallenden Taktflanke nach dem Stoppbit der Schreibtransaktion.

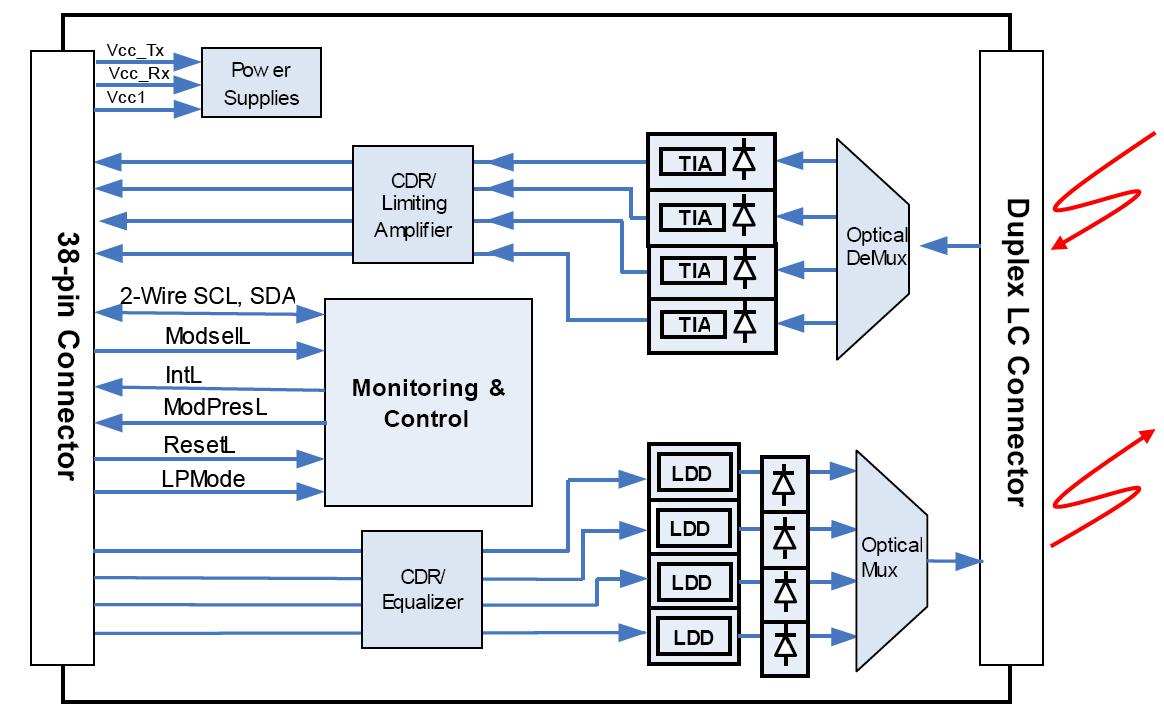

•Blockdiagramm des Transceivers

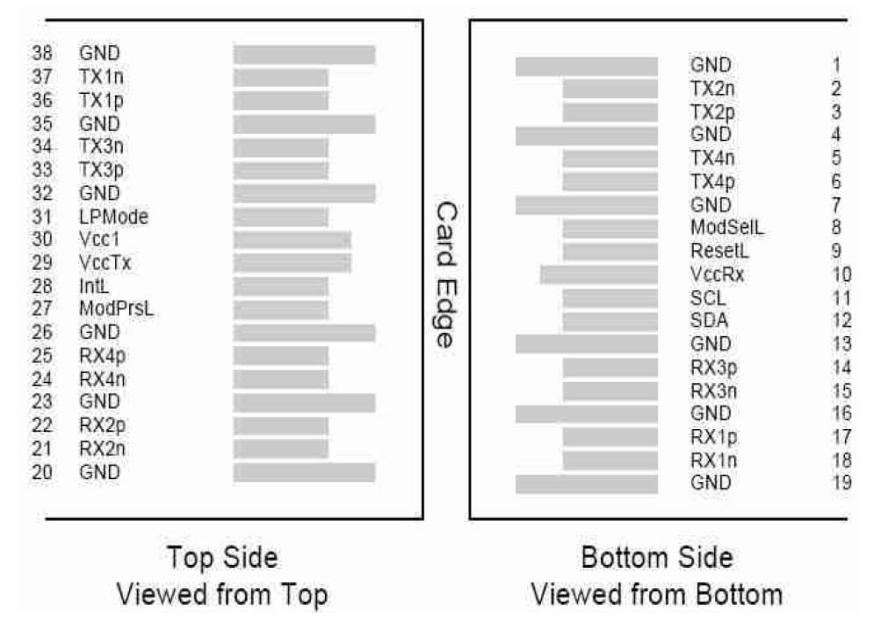

•Pin-Belegung

Diagramm der Pin-Nummern und Namen des Host-Board-Anschlussblocks

•StiftBeschreibung

| Stift | Logik | Symbol | Name/Beschreibung | Ref. |

| 1 |

| GND | Boden | 1 |

| 2 | CML-I | Tx2n | Invertierter Dateneingang des Senders |

|

| 3 | CML-I | Tx2p | Nicht invertierter Datenausgang des Senders |

|

| 4 |

| GND | Boden | 1 |

| 5 | CML-I | Tx4n | Invertierter Datenausgang des Senders |

|

| 6 | CML-I | Tx4p | Nicht invertierter Datenausgang des Senders |

|

| 7 |

| GND | Boden | 1 |

| 8 | LVTTL-I | ModSelL | Modulauswahl |

|

| 9 | LVTTL-I | ZurücksetzenL | Modul-Reset |

|

| 10 |

| VccRx | +3,3-V-Stromversorgungsempfänger | 2 |

| 11 | LVCMOS-I/O | SCL | 2-Draht-Seriellschnittstellenuhr |

|

| 12 | LVCMOS-I/O | SDA | Daten der seriellen 2-Draht-Schnittstelle |

|

| 13 |

| GND | Boden | 1 |

| 14 | CML-O | Rx3p | Invertierter Datenausgang des Empfängers |

|

| 15 | CML-O | Rx3n | Nicht invertierte Datenausgabe des Empfängers |

|

| 16 |

| GND | Boden | 1 |

| 17 | CML-O | Rx1p | Invertierter Datenausgang des Empfängers |

|

| 18 | CML-O | Rx1n | Nicht invertierte Datenausgabe des Empfängers |

|

| 19 |

| GND | Boden | 1 |

| 20 |

| GND | Boden | 1 |

| 21 | CML-O | Rx2n | Invertierter Datenausgang des Empfängers |

|

| 22 | CML-O | Rx2p | Nicht invertierte Datenausgabe des Empfängers |

|

| 23 |

| GND | Boden | 1 |

| 24 | CML-O | Rx4n | Invertierter Datenausgang des Empfängers |

|

| 25 | CML-O | Rx4p | Nicht invertierte Datenausgabe des Empfängers |

|

| 26 |

| GND | Boden | 1 |

| 27 | LVTTL-O | ModPrsL | Modul vorhanden |

|

| 28 | LVTTL-O | IntL | Unterbrechen |

|

| 29 |

| VccTx | +3,3-V-Stromversorgungssender | 2 |

| 30 |

| Vcc1 | +3,3-V-Stromversorgung | 2 |

| 31 | LVTTL-I | LPMode | Energiesparmodus |

|

| 32 |

| GND | Boden | 1 |

| 33 | CML-I | Tx3p | Invertierter Datenausgang des Senders |

|

| 34 | CML-I | Tx3n | Nicht invertierter Datenausgang des Senders |

|

| 35 |

| GND | Boden | 1 |

| 36 | CML-I | Tx1p | Invertierter Datenausgang des Senders |

|

| 37 | CML-I | Tx1n | Nicht invertierter Datenausgang des Senders |

|

| 38 |

| GND | Boden | 1 |

Anmerkungen:

- GND ist das Symbol für Single und Supply(Power) Common für QSFP28-Module. Im QSFP28-Modul sind alle gemeinsam und alle Modulspannungen beziehen sich auf dieses Potenzial, sofern nicht anders angegeben.Verbinden Sie diese direkt mit der gemeinsamen Signalerdungsebene der Hostplatine.Laserausgang deaktiviert bei TDIS >2,0 V oder offen, aktiviert bei TDIS <0,8 V.

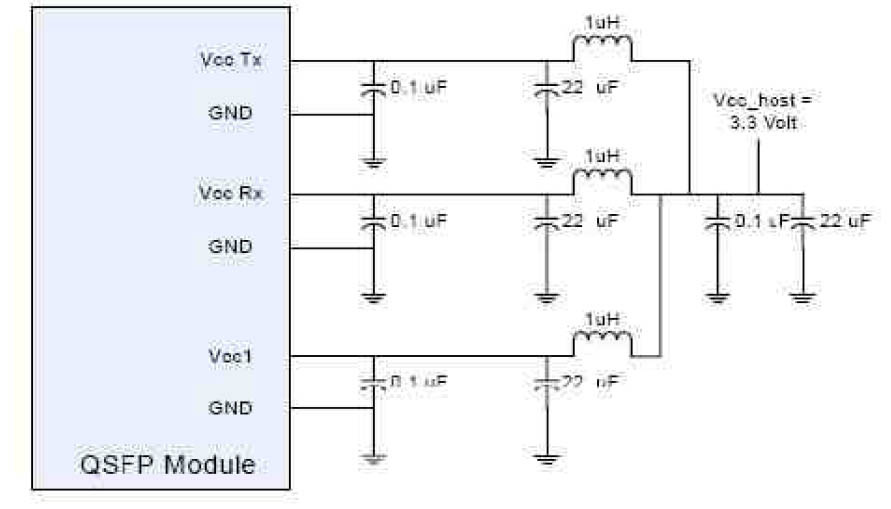

- VccRx, Vcc1 und VccTx sind die Empfänger- und Senderstromlieferanten und müssen gleichzeitig angewendet werden.Die empfohlene Filterung des Host-Board-Netzteils ist unten aufgeführt.VccRx, Vcc1 und VccTx können innerhalb des QSFP28-Transceivermoduls in beliebiger Kombination intern verbunden werden.Die Anschlussstifte sind jeweils für einen maximalen Strom von 500 mA ausgelegt.

•Empfohlene Schaltung

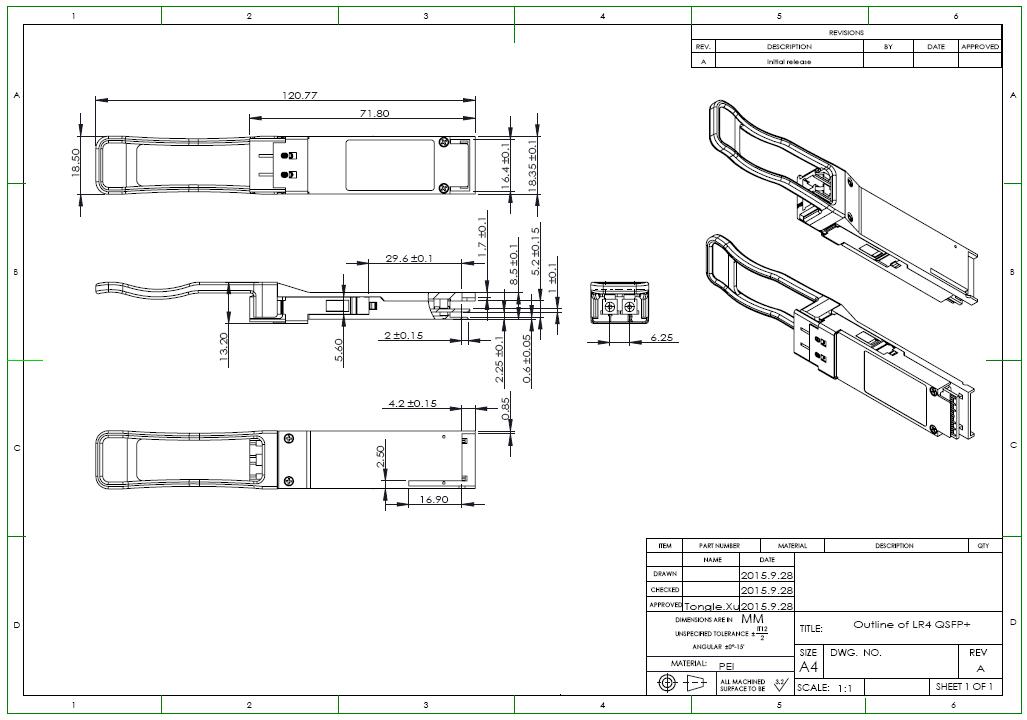

•Mechanische Abmessungen