40G QSFP+ SR4, 300 m MPO 850 nm JHAQC01

Merkmale:

◊ Entspricht der elektrischen 40GbE XLPPI-Spezifikation gemäß IEEE 802.3ba-2010

◊ Konform mit der QSFP+ SFF-8436-Spezifikation

◊ Gesamtbandbreite von > 40 Gbit/s

◊ Arbeitet mit 10,3125 Gbit/s pro elektrischem Kanal mit 64b/66b-codierten Daten

◊ QSFP MSA-konform

◊ Ermöglicht eine Übertragung von über 100 m auf OM3 Multimode Fiber (MMF) und 150 m auf OM4 MMF

◊ Einzelnes +3,3-V-Netzteil in Betrieb

◊ Ohne digitale Diagnosefunktionen

◊ Temperaturbereich 0°C bis 70°C

◊ RoHS-konformes Teil

◊ Verwendet ein Standard-LC-Duplex-Glasfaserkabel, das die Wiederverwendung vorhandener Kabelinfrastruktur ermöglicht

Anwendungen:

◊ 40 Gigabit-Ethernet-Verbindungen

◊ Daten-/Telekommunikations-Switch- und Router-Verbindungen

◊ Datenaggregation und Backplane-Anwendungen

◊ Proprietäre Protokoll- und Dichteanwendungen

Beschreibung:

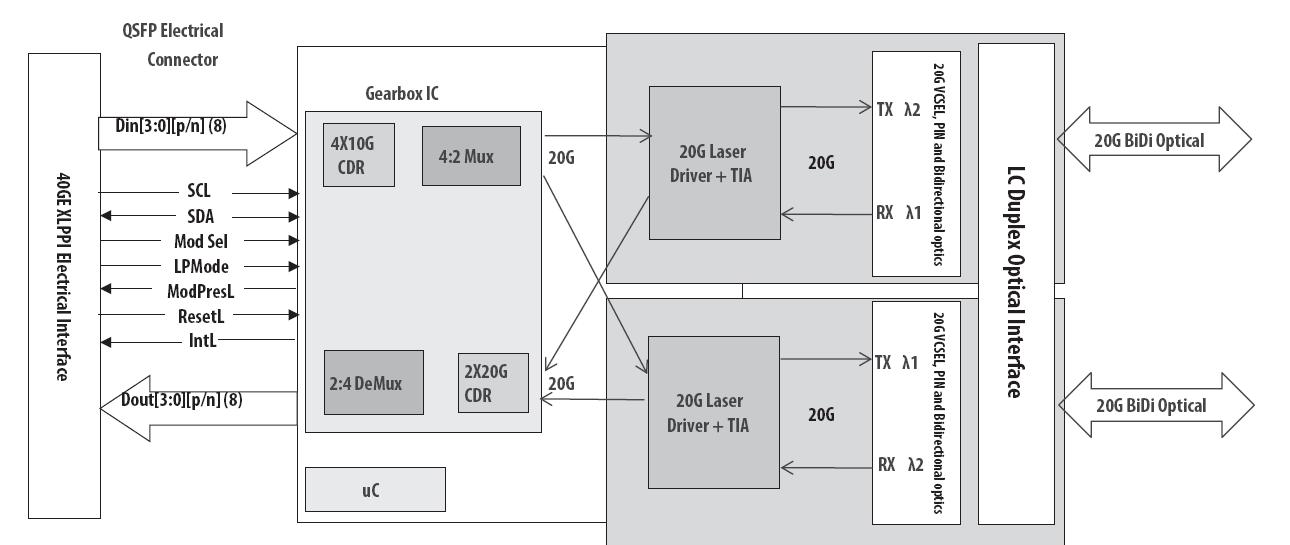

Es handelt sich um einen vierkanaligen, steckbaren LC-Duplex-Glasfaser-QSFP+-Transceiver für 40-Gigabit-Ethernet-Anwendungen.Dieser Transceiver ist ein Hochleistungsmodul für Duplex-Datenkommunikation und Verbindungsanwendungen mit kurzer Reichweite.Es integriert vier elektrische Datenspuren in jede Richtung in die Übertragung über ein einziges LC-Duplex-Glasfaserkabel.Jede elektrische Leitung arbeitet mit 10,3125 Gbit/s und entspricht der 40GE XLPPI-Schnittstelle.

Der Transceiver multiplext intern eine XLPPI 4x10G-Schnittstelle in zwei elektrische Kanäle mit 20 Gbit/s und sendet und empfängt jeweils optisch über eine Simplex-LC-Faser mit bidirektionaler Optik.Dies führt zu einer Gesamtbandbreite von 40 Gbit/s in einem Duplex-LC-Kabel.Dies ermöglicht die Wiederverwendung der installierten LC-Duplex-Verkabelungsinfrastruktur für 40-GbE-Anwendungen.Verbindungsentfernungen bis zu 100 m mit OM3 und 150 m mit OM4-Glasfaser werden unterstützt.Diese Module sind für den Betrieb über Multimode-Glasfasersysteme mit einer Nennwellenlänge von 850 nm an einem Ende und 900 nm am anderen Ende ausgelegt.Die elektrische Schnittstelle verwendet einen Randsteckverbinder vom Typ QSFP+ mit 38 Kontakten.Die optische Schnittstelle nutzt einen herkömmlichen LC-Duplex-Stecker.

Blockdiagramm des Transceivers

•absolut beste Bewertungen

| Parameter | Symbol | Mindest. | Typisch | Max. | Einheit |

| Lagertemperatur | TS | -40 |

| +85 | °C |

| Versorgungsspannung | VCCT, R | -0,5 |

| 4 | V |

| Relative Luftfeuchtigkeit | RH | 0 |

| 85 | % |

•EmpfohlenBetriebsumgebung:

| Parameter | Symbol | Mindest. | Typisch | Max. | Einheit |

| Gehäusebetriebstemperatur | TC | 0 |

| +70 | °C |

| Versorgungsspannung | VCCT, R | +3.13 | 3.3 | +3,47 | V |

| Versorgungsstrom | ICC |

|

| 1000 | mA |

| Energieverschwendung | PD |

|

| 3.5 | W |

•Elektrische Eigenschaften(TOP = 0 bis 70 °C, VCC = 3,13 bis 3,47 Volt

| Parameter | Symbol | Mindest | Typ | Max | Einheit | Notiz |

| Datenrate pro Kanal |

| - | 10.3125 | 11.2 | Gbit/s |

|

| Energieverbrauch |

| - | 2.5 | 3.5 | W |

|

| Versorgungsstrom | Icc |

| 0,75 | 1,0 | A |

|

| Steuer-E/A-Spannung hoch | VIH | 2,0 |

| Vcc | V |

|

| Steuer-E/A-Spannung niedrig | VIL | 0 |

| 0,7 | V |

|

| Inter-Channel-Skew | TSK |

|

| 150 | Ps |

|

| RESETL-Dauer |

|

| 10 |

| Us |

|

| RESETL Deaktivierungszeit |

|

|

| 100 | ms |

|

| Einschaltzeit |

|

|

| 100 | ms |

|

| Sender | ||||||

| Single-Ended-Ausgangsspannungstoleranz |

| 0,3 |

| 4 | V | 1 |

| Gleichtaktspannungstoleranz |

| 15 |

|

| mV |

|

| Eingangsdifferenzspannung übertragen | VI | 120 |

| 1200 | mV |

|

| Differenzimpedanz des Sendeeingangs | ZIN | 80 | 100 | 120 |

|

|

| Datenabhängiger Eingabe-Jitter | DDJ |

|

| 0,1 | UI |

|

| Gesamtjitter der Dateneingabe | TJ |

|

| 0,28 | UI |

|

| Empfänger | ||||||

| Single-Ended-Ausgangsspannungstoleranz |

| 0,3 |

| 4 | V |

|

| Rx-Ausgangsdifferenzspannung | Vo |

| 600 | 800 | mV |

|

| Anstiegs- und Abfallspannung des Rx-Ausgangs | Tr/Tf |

|

| 35 | ps | 1 |

| Totaler Jitter | TJ |

|

| 0,7 | UI |

|

| Deterministischer Jitter | DJ |

|

| 0,42 | UI |

|

Notiz:

- 20~80 %

•Optische Parameter (TOP = 0 bis 70°C, VCC = 3,0 bis 3,6 Volt)

| Parameter | Symbol | Mindest | Typ | Max | Einheit | Ref. |

| Sender | ||||||

| Optische Wellenlänge CH1 | λ | 832 | 850 | 868 | nm |

|

| Optische Wellenlänge CH2 | λ | 882 | 900 | 918 | nm |

|

| RMS-Spektralbreite | Pm |

| 0,5 | 0,65 | nm |

|

| Durchschnittliche optische Leistung pro Kanal | Pavg | -4 | -2,5 | +5,0 | dBm |

|

| Laser-Aus-Leistung pro Kanal | Poff |

|

| -30 | dBm |

|

| Optisches Extinktionsverhältnis | ER | 3.5 |

|

| dB |

|

| Relatives Intensitätsrauschen | Rin |

|

| -128 | dB/Hz | 1 |

| Toleranz der optischen Rückflussdämpfung |

|

|

| 12 | dB |

|

| Empfänger | ||||||

| Optische Mittenwellenlänge CH1 | λ | 882 | 900 | 918 | nm |

|

| Optische Mittenwellenlänge CH2 | λ | 832 | 850 | 868 | nm |

|

| Empfängerempfindlichkeit pro Kanal | R |

| -11 |

| dBm |

|

| Maximale Eingangsleistung | PMAX | +0,5 |

|

| dBm |

|

| Reflexionsgrad des Empfängers | Rrx |

|

| -12 | dB |

|

| LOS De-Assert | LOSD |

|

| -14 | dBm |

|

| LOS-Bestätigung | LOSA | -30 |

|

| dBm |

|

| LOS-Hysterese | LOSH | 0,5 |

|

| dB |

|

Notiz

- 12 dB Reflexion

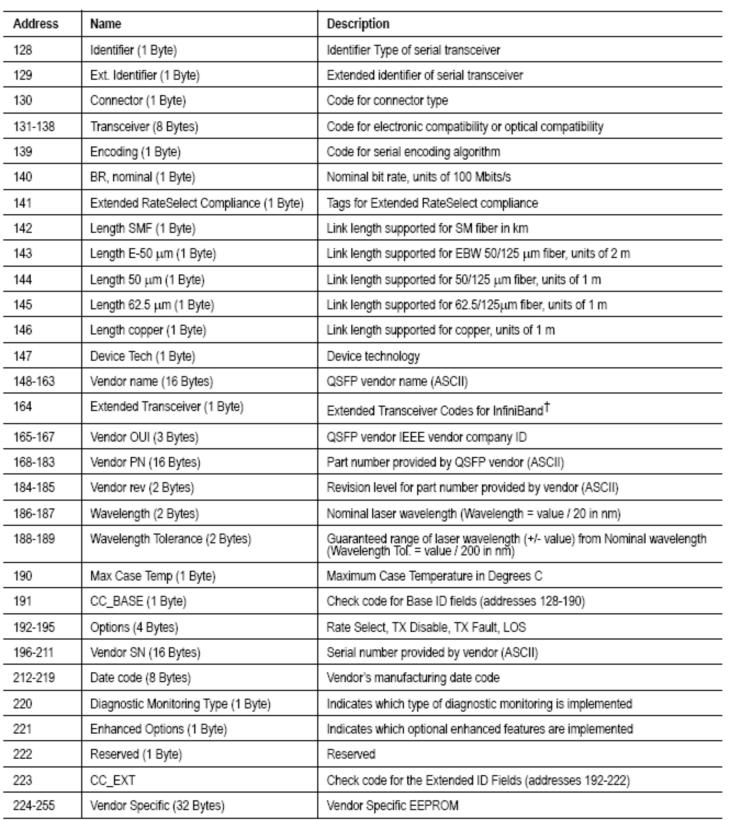

Seite02 ist das Benutzer-EEPROM und sein Format wird vom Benutzer festgelegt.

Die detaillierte Beschreibung von „Low Memory“ und „Page00.page03 Upper Memory“ finden Sie im SFF-8436-Dokument.

•Timing für Soft-Control- und Statusfunktionen

| Parameter | Symbol | Max | Einheit | Bedingungen |

| Initialisierungszeit | t_init | 2000 | ms | Zeit vom Einschalten1, Hot-Plug oder steigender Reset-Flanke bis zur vollständigen Funktionsfähigkeit des Moduls2 |

| Setzen Sie die Init-Assert-Zeit zurück | t_reset_init | 2 | μs | Ein Reset wird durch einen Low-Pegel erzeugt, der länger als die minimale Reset-Impulszeit am ResetL-Pin liegt. |

| Bereitschaftszeit der seriellen Bus-Hardware | t_serial | 2000 | ms | Zeit vom Einschalten1 bis das Modul auf die Datenübertragung über den seriellen 2-Draht-Bus reagiert |

| Monitordaten bereitZeit | t_data | 2000 | ms | Zeit vom Einschalten1 bis zur Nichtbereitstellung der Daten, Bit 0 von Byte 2, deaktiviert und IntL aktiviert |

| Setzen Sie die Bestätigungszeit zurück | t_reset | 2000 | ms | Zeit von der steigenden Flanke am ResetL-Pin bis zur vollständigen Funktionsfähigkeit des Moduls2 |

| LPMode-Assert-Zeit | ton_LPMode | 100 | μs | Zeit von der Aktivierung des LPMode (Vin:LPMode =Vih), bis der Stromverbrauch des Moduls einen niedrigeren Leistungspegel erreicht |

| IntL-Bestätigungszeit | ton_IntL | 200 | ms | Zeit vom Eintreten der Bedingung, die IntL auslöst, bis Vout:IntL = Vol |

| IntL Deaktivierungszeit | toff_IntL | 500 | μs | toff_IntL 500 μs Zeit vom Löschen des Lese3-Vorgangs des zugehörigen Flags bis Vout:IntL = Voh.Dazu gehören Deaktivierungszeiten für Rx LOS, Tx Fault und andere Flag-Bits. |

| Rx LOS Assert-Zeit | ton_los | 100 | ms | Zeit vom Rx-LOS-Zustand bis zum Setzen des Rx-LOS-Bits und der Bestätigung von IntL |

| Flag-Assert-Zeit | ton_flag | 200 | ms | Zeit vom Auftreten des bedingungsauslösenden Flags bis zum Setzen des zugehörigen Flag-Bits und der Geltendmachung von IntL |

| Mask-Assert-Zeit | ton_mask | 100 | ms | Zeit vom Setzen des Maskenbits4 bis zur Sperrung der zugehörigen IntL-Assertion |

| Mask-Deaktivierungszeit | toff_mask | 100 | ms | Zeit vom Löschen des Maskenbits4 bis zur Wiederaufnahme des zugehörigen IntlL-Vorgangs |

| ModSelL Assert-Zeit | ton_ModSelL | 100 | μs | Zeit von der Aktivierung von ModSelL bis zur Reaktion des Moduls auf die Datenübertragung über den seriellen 2-Draht-Bus |

| ModSelL-Deaktivierungszeit | toff_ModSelL | 100 | μs | Zeit von der Aufhebung von ModSelL bis das Modul nicht mehr auf die Datenübertragung über den seriellen 2-Draht-Bus reagiert |

| Power_over-ride oderPower-Set-Assert-Zeit | ton_Pdown | 100 | ms | Zeit vom Setzen des P_Down-Bits 4 bis zum Erreichen des niedrigeren Leistungsniveaus des Modulstromverbrauchs |

| Power_over-ride oder Power-set De-assert Time | toff_Pdown | 300 | ms | Zeit vom Löschen des P_Down-Bits4 bis zur vollständigen Funktionsfähigkeit des Moduls3 |

Notiz::

1. Einschalten ist definiert als der Moment, in dem die Versorgungsspannungen den angegebenen Mindestwert erreichen und auf diesem oder darüber bleiben.

2. Voll funktionsfähig ist definiert als IntL aktiviert aufgrund des Daten-nicht-bereit-Bits, Bit 0 Byte 2 deaktiviert.

3. Gemessen ab der fallenden Taktflanke nach dem Stoppbit der Lesetransaktion.

4. Gemessen ab der fallenden Taktflanke nach dem Stoppbit der Schreibtransaktion.

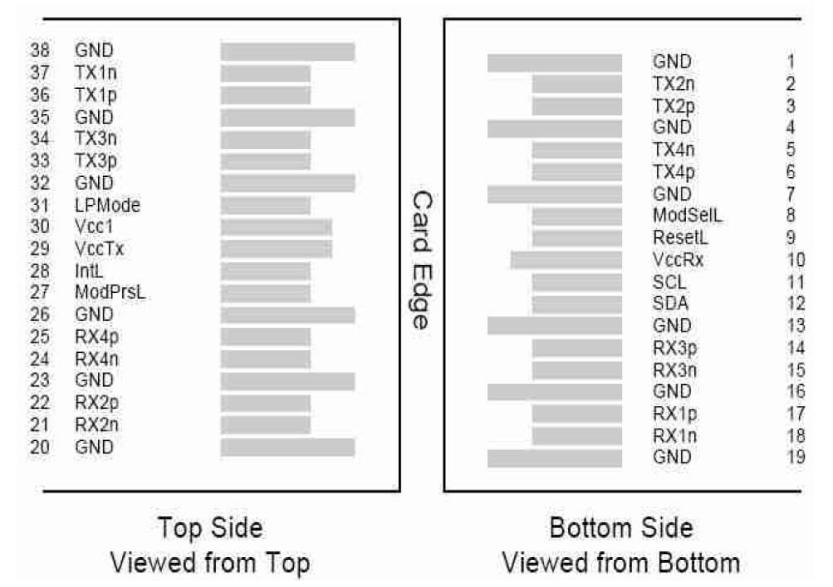

•Pin-Belegung

Diagramm der Pin-Nummern und Namen des Host-Board-Anschlussblocks

• PinBeschreibung

| Stift | Logik | Symbol | Name/Beschreibung | Ref. |

| 1 |

| GND | Boden | 1 |

| 2 | CML-I | Tx2n | Invertierter Dateneingang des Senders |

|

| 3 | CML-I | Tx2p | Nicht invertierter Datenausgang des Senders |

|

| 4 |

| GND | Boden | 1 |

| 5 | CML-I | Tx4n | Invertierter Datenausgang des Senders |

|

| 6 | CML-I | Tx4p | Nicht invertierter Datenausgang des Senders |

|

| 7 |

| GND | Boden | 1 |

| 8 | LVTTL-I | ModSelL | Modulauswahl |

|

| 9 | LVTTL-I | ZurücksetzenL | Modul-Reset |

|

| 10 |

| VccRx | +3,3-V-Stromversorgungsempfänger | 2 |

| 11 | LVCMOS-I/O | SCL | 2-Draht-Seriellschnittstellenuhr |

|

| 12 | LVCMOS-I/O | SDA | Daten der seriellen 2-Draht-Schnittstelle |

|

| 13 |

| GND | Boden | 1 |

| 14 | CML-O | Rx3p | Invertierter Datenausgang des Empfängers |

|

| 15 | CML-O | Rx3n | Nicht invertierte Datenausgabe des Empfängers |

|

| 16 |

| GND | Boden | 1 |

| 17 | CML-O | Rx1p | Invertierter Datenausgang des Empfängers |

|

| 18 | CML-O | Rx1n | Nicht invertierte Datenausgabe des Empfängers |

|

| 19 |

| GND | Boden | 1 |

| 20 |

| GND | Boden | 1 |

| 21 | CML-O | Rx2n | Invertierter Datenausgang des Empfängers |

|

| 22 | CML-O | Rx2p | Nicht invertierte Datenausgabe des Empfängers |

|

| 23 |

| GND | Boden | 1 |

| 24 | CML-O | Rx4n | Invertierter Datenausgang des Empfängers |

|

| 25 | CML-O | Rx4p | Nicht invertierte Datenausgabe des Empfängers |

|

| 26 |

| GND | Boden | 1 |

| 27 | LVTTL-O | ModPrsL | Modul vorhanden |

|

| 28 | LVTTL-O | IntL | Unterbrechen |

|

| 29 |

| VccTx | +3,3-V-Stromversorgungssender | 2 |

| 30 |

| Vcc1 | +3,3-V-Stromversorgung | 2 |

| 31 | LVTTL-I | LPMode | Energiesparmodus |

|

| 32 |

| GND | Boden | 1 |

| 33 | CML-I | Tx3p | Invertierter Datenausgang des Senders |

|

| 34 | CML-I | Tx3n | Nicht invertierter Datenausgang des Senders |

|

| 35 |

| GND | Boden | 1 |

| 36 | CML-I | Tx1p | Invertierter Datenausgang des Senders |

|

| 37 | CML-I | Tx1n | Nicht invertierter Datenausgang des Senders |

|

| 38 |

| GND | Boden | 1 |

Anmerkungen:

- GND ist das Symbol für Single und Supply(Power) Common für QSFP-Module. Alle sind innerhalb des QSFP-Moduls gemeinsam und alle Modulspannungen beziehen sich auf dieses Potenzial, sofern nicht anders angegeben.Verbinden Sie diese direkt mit der gemeinsamen Signalerdungsebene der Hostplatine.Laserausgang deaktiviert bei TDIS >2,0 V oder offen, aktiviert bei TDIS <0,8 V.

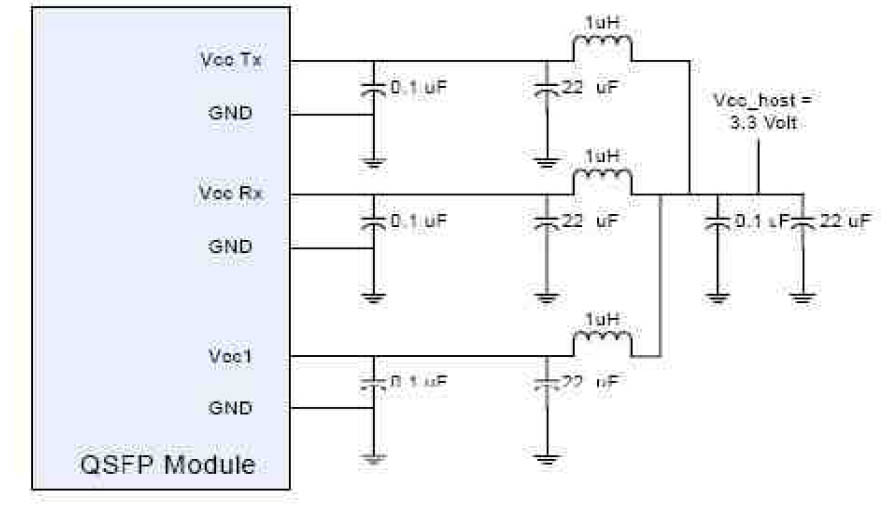

- VccRx, Vcc1 und VccTx sind die Empfänger- und Senderstromlieferanten und müssen gleichzeitig angewendet werden.Die empfohlene Filterung des Host-Board-Netzteils ist unten aufgeführt.VccRx, Vcc1 und VccTx können innerhalb des QSFP-Transceivermoduls in beliebiger Kombination intern verbunden werden.Die Anschlussstifte sind jeweils für einen maximalen Strom von 500 mA ausgelegt.

•Empfohlene Schaltung

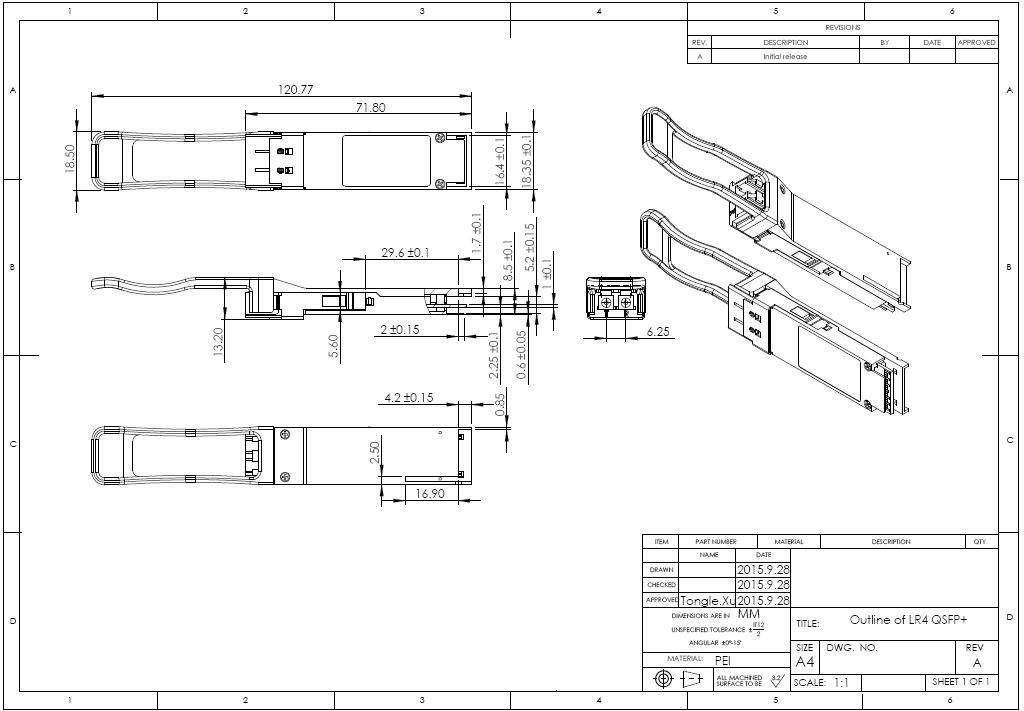

Mechanische Abmessungen