40G QSFP+ SR4၊ 300m MPO 850nm JHAQC01

အင်္ဂါရပ်များ:

◊ IEEE 802.3ba-2010 အရ 40GbE XLPPI လျှပ်စစ်သတ်မှတ်ချက်နှင့် ကိုက်ညီသည်

◊ QSFP+ SFF-8436 သတ်မှတ်ချက်နှင့် ကိုက်ညီသည်။

◊ စုစုပေါင်း Bandwidth > 40Gbps

◊ လျှပ်စစ်ချန်နယ်တစ်ခုလျှင် 10.3125 Gbps နှုန်းဖြင့် 64b/66b ကုဒ်နံပါတ်ဖြင့် လုပ်ဆောင်သည်

◊ QSFP MSA နှင့် ကိုက်ညီသည်။

◊ OM3 Multimode Fiber (MMF) နှင့် OM4 MMF တွင် မီတာ 150 ကျော် ထုတ်လွှင့်နိုင်စွမ်း

◊ တစ်ခုတည်း +3.3V ပါဝါထောက်ပံ့မှု လည်ပတ်ခြင်း။

◊ ဒစ်ဂျစ်တယ်ရောဂါရှာဖွေရေးလုပ်ဆောင်ချက်များမပါဘဲ

◊ အပူချိန် 0°C မှ 70°C အထိ

◊ RoHS လိုက်နာမှုအပိုင်း

◊ ရှိပြီးသားကေဘယ်အခြေခံအဆောက်အအုံကို ပြန်လည်အသုံးပြုခွင့်ပြုသည့် Standard LC Duplex Fiber Cable ကို အသုံးပြုသည်။

လျှောက်လွှာများ:

◊ 40 Gigabit Ethernet အပြန်အလှန်ချိတ်ဆက်သည်။

◊ Datacom/Telecom ခလုတ်နှင့် router ချိတ်ဆက်မှုများ

◊ ဒေတာစုပေါင်းခြင်းနှင့် နောက်ကြောင်းပြန်ပျံအပလီကေးရှင်းများ

◊ မူပိုင်ပရိုတိုကောနှင့် သိပ်သည်းဆ အသုံးချပရိုဂရမ်များ

ဖော်ပြချက်-

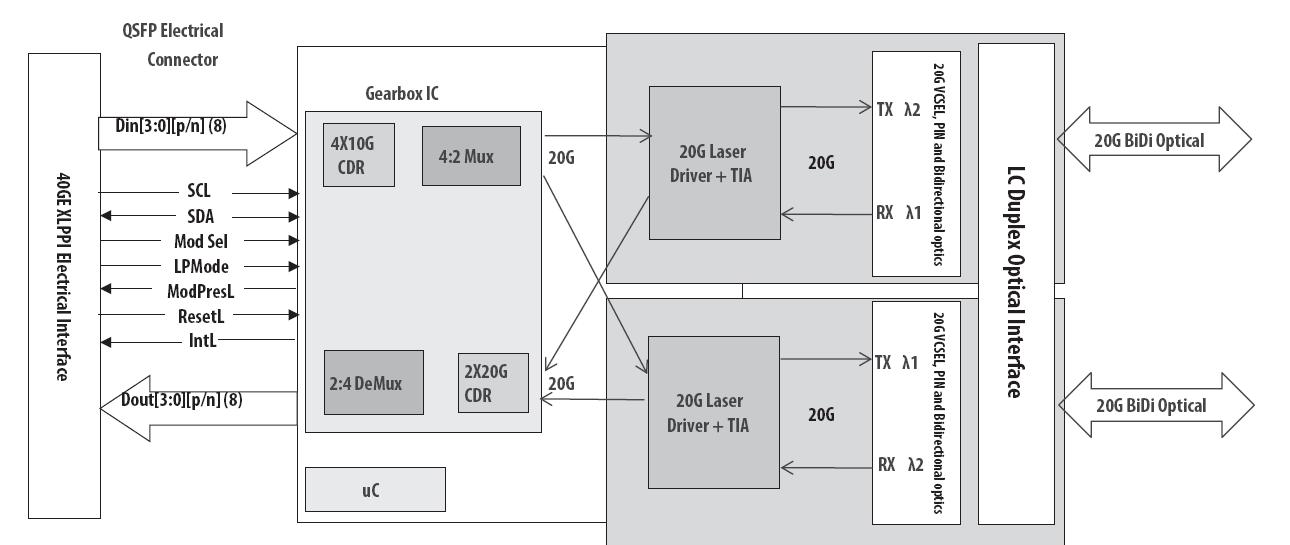

၎င်းသည် 40 Gigabit Ethernet Applications အတွက် Four-Channel၊ Pluggable၊ LC Duplex၊ Fiber-Optic QSFP+ Transceiver ဖြစ်သည်။ဤ transceiver သည် short-range duplex data communication နှင့် interconnect applications များအတွက် စွမ်းဆောင်ရည်မြင့် module တစ်ခုဖြစ်သည်။၎င်းသည် ဦးတည်ချက်တစ်ခုစီတွင် လျှပ်စစ်ဒေတာလမ်းကြောင်းလေးခုကို LC Duplex Fiber Optic Cable တစ်ခုတည်းမှ ထုတ်လွှင့်ခြင်းသို့ ပေါင်းစပ်ထားသည်။လျှပ်စစ်လမ်းကြောတစ်ခုစီသည် 10.3125 Gbps ဖြင့် လည်ပတ်ပြီး 40GE XLPPI အင်တာဖေ့စ်နှင့် ကိုက်ညီသည်။

transceiver သည် အတွင်းတွင် multiplex ဖြစ်သော XLPPI 4x10G အင်တာဖေ့စ်ကို 20Gb/s လျှပ်စစ်ချန်နယ်နှစ်ခုသို့ ထုတ်ပေးပြီး တစ်ခုစီကို ရိုးရှင်းသော LC ဖိုက်ဘာတစ်ခုမှ optically တစ်ခုစီသို့ ပို့ကာ လက်ခံသည်။၎င်းသည် စုစုပေါင်း bandwidth 40Gbps ကို duplex LC ကေဘယ်သို့ ဖြစ်စေသည်။၎င်းသည် 40GbE အပလီကေးရှင်းအတွက် တပ်ဆင်ထားသည့် LC duplex ကေဘယ်လ်အခြေခံအဆောက်အအုံကို ပြန်လည်အသုံးပြုခွင့်ပြုသည်။OM4 optical fiber ကို အသုံးပြု၍ OM3 နှင့် 150m ကိုအသုံးပြု၍ 100 m အကွာအဝေးအထိ လင့်ခ်အကွာအဝေးကို ပံ့ပိုးထားပါသည်။ဤမော်ဂျူးများသည် တစ်ဖက်မှ 850nm နှင့် အခြားတစ်ဖက်တွင် 900nm အမည်ခံလှိုင်းအလျားကို အသုံးပြု၍ multimode ဖိုက်ဘာစနစ်များပေါ်တွင် လုပ်ဆောင်ရန် ဒီဇိုင်းထုတ်ထားသည်။လျှပ်စစ်မျက်နှာပြင်သည် 38 အဆက်အသွယ် QSFP+ အမျိုးအစား အစွန်းချိတ်ဆက်ကိရိယာကို အသုံးပြုသည်။optical interface သည် သမားရိုးကျ LC duplex connector ကိုအသုံးပြုသည်။

Transceiver Block Diagram

•အကြွင်းမဲ့ အများဆုံး အဆင့်သတ်မှတ်ချက်များ

| ကန့်သတ်ချက် | သင်္ကေတ | မင်း | ပုံမှန် | မက်တယ်။ | ယူနစ် |

| သိုလှောင်မှုအပူချိန် | TS | စာ-၄၀ |

| +၈၅ | °C |

| ထောက်ပံ့ရေးဗို့အား | VCCT၊ R | -0.5 |

| 4 | V |

| နှိုင်းရစိုထိုင်းဆ | RH | 0 |

| 85 | % |

•အကြံပြုသည်။လည်ပတ်မှုပတ်ဝန်းကျင်-

| ကန့်သတ်ချက် | သင်္ကေတ | မင်း | ပုံမှန် | မက်တယ်။ | ယူနစ် |

| Case လည်ပတ်မှု အပူချိန် | TC | 0 |

| +70 | °C |

| ထောက်ပံ့ရေးဗို့အား | VCCT, R | +၃.၁၃ | ၃.၃ | +၃.၄၇ | V |

| ထောက်ပံ့ရေးလက်ရှိ | ICC |

|

| ၁၀၀၀ | mA |

| ပါဝါ Dissipation | PD |

|

| ၃.၅ | W |

•လျှပ်စစ်လက္ခဏာများ(TOP = 0 မှ 70°C၊ VCC = 3.13 မှ 3.47 ဗို့

| ကန့်သတ်ချက် | သင်္ကေတ | မင်း | စာရိုက်ပါ။ | မက်တယ်။ | ယူနစ် | မှတ်ချက် |

| ချန်နယ်တစ်ခုအတွက် ဒေတာနှုန်း |

| - | ၁၀.၃၁၂၅ | ၁၁.၂ | Gbps |

|

| ပါဝါစားသုံးမှု |

| - | ၂.၅ | ၃.၅ | W |

|

| ထောက်ပံ့ရေးလက်ရှိ | Icc |

| ၀.၇၅ | ၁.၀ | A |

|

| I/O Voltage-High ကို ထိန်းချုပ်ပါ။ | VIH | 2.0 |

| Vcc | V |

|

| I/O Voltage-Low ကို ထိန်းချုပ်ပါ။ | VIL | 0 |

| ၀.၇ | V |

|

| Inter-Channel Skew | TSK |

|

| ၁၅၀ | Ps |

|

| RESETL ကြာချိန် |

|

| 10 |

| Us |

|

| အခိုင်အမာအချိန်ကို ပြန်လည်သတ်မှတ်ပါ။ |

|

|

| ၁၀၀ | ms |

|

| ပါဝါဖွင့်ချိန် |

|

|

| ၁၀၀ | ms |

|

| Transmitter | ||||||

| Single Ended Output Voltage Tolerance |

| ၀.၃ |

| 4 | V | 1 |

| အသုံးများသောမုဒ်တွင် Voltage Tolerance |

| 15 |

|

| mV |

|

| Transmit Input Diff Voltage | VI | ၁၂၀ |

| ၁၂၀၀ | mV |

|

| Transmit Input Diff Impedance | ZIN | 80 | ၁၀၀ | ၁၂၀ |

|

|

| Data Dependent Input Jitter | DDJ |

|

| ၀.၁ | UI |

|

| ဒေတာထည့်သွင်းမှု စုစုပေါင်းတုန်လှုပ်ခြင်း။ | TJ |

|

| ၀.၂၈ | UI |

|

| လက်ခံသူ | ||||||

| Single Ended Output Voltage Tolerance |

| ၀.၃ |

| 4 | V |

|

| Rx Output Diff Voltage | Vo |

| ၆၀၀ | ၈၀၀ | mV |

|

| Rx Output Rise နှင့် Fall Voltage | Tr/Tf |

|

| 35 | ps | 1 |

| စုစုပေါင်းတုန် | TJ |

|

| ၀.၇ | UI |

|

| Deterministic Jitter | DJ |

|

| ၀.၄၂ | UI |

|

မှတ်ချက် -

- 20~80%

•Optical Parameters(TOP = 0 မှ 70 အထိ°C၊ VCC = 3.0 မှ 3.6 ဗို့)

| ကန့်သတ်ချက် | သင်္ကေတ | မင်း | စာရိုက်ပါ။ | မက်တယ်။ | ယူနစ် | Ref. |

| Transmitter | ||||||

| Optical Wavelength CH1 | λ | ၈၃၂ | ၈၅၀ | ၈၆၈ | nm |

|

| Optical Wavelength CH2 | λ | ၈၈၂ | ၉၀၀ | ၉၁၈ | nm |

|

| RMS Spectral Width | Pm |

| ၀.၅ | ၀.၆၅ | nm |

|

| Channel တစ်ခုအတွက် ပျမ်းမျှ Optical Power | Pavg | -4 | -၂.၅ | +5.0 | dBm |

|

| ချန်နယ်အလိုက် လေဆာပါဝါပိတ် | Poff |

|

| စာ-၃၀ | dBm |

|

| Optical Extinction Ratio | ER | ၃.၅ |

|

| dB |

|

| Relative Intensity ဆူညံသံ | ရင် |

|

| စာ-၁၂၈ | dB/HZ | 1 |

| Optical Return Loss Tolerance |

|

|

| 12 | dB |

|

| လက်ခံသူ | ||||||

| Optical Center Wavelength CH1 | λ | ၈၈၂ | ၉၀၀ | ၉၁၈ | nm |

|

| Optical Center Wavelength CH2 | λ | ၈၃၂ | ၈၅၀ | ၈၆၈ | nm |

|

| ချန်နယ်အလိုက် လက်ခံသူ အာရုံခံနိုင်စွမ်း | R |

| စာ-၁၁ |

| dBm |

|

| အများဆုံးထည့်သွင်းပါဝါ | PMAX | +0.5 |

|

| dBm |

|

| လက်ခံသူ ရောင်ပြန်ဟပ်မှု | Rrx |

|

| စာ-၁၂ | dB |

|

| တကယ်ဆို De-Assert | တကယ်ဆိုD |

|

| စာ-၁၄ | dBm |

|

| တကယ်ဆို အခိုင်အမာ | တကယ်ဆိုA | စာ-၃၀ |

|

| dBm |

|

| တကယ်ဆို Hysteresis | တကယ်ဆိုH | ၀.၅ |

|

| dB |

|

မှတ်ချက်

- 12dB ရောင်ပြန်ဟပ်မှု

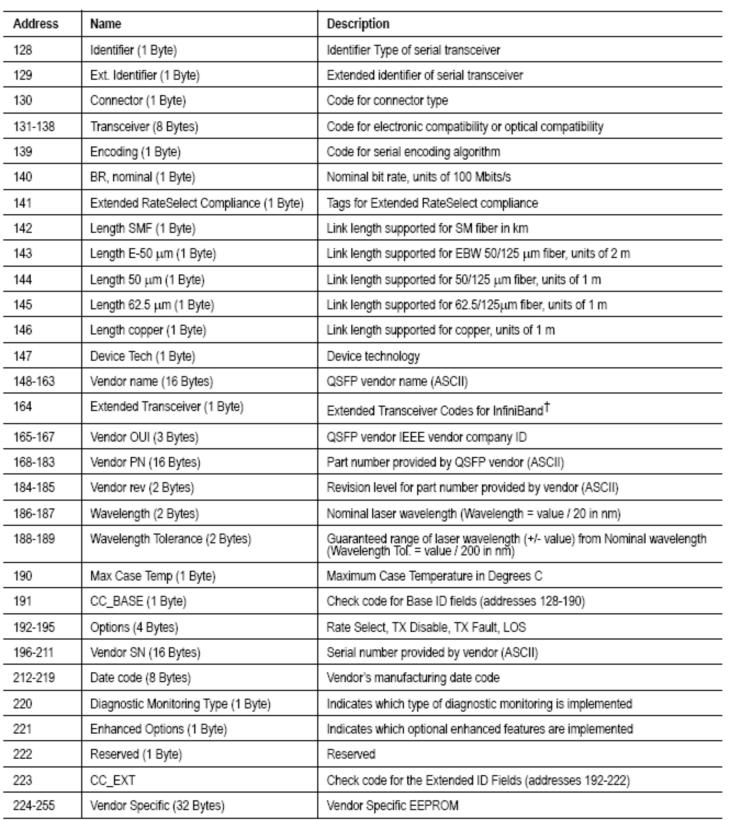

Page02 သည် အသုံးပြုသူ EEPROM ဖြစ်ပြီး ၎င်း၏ဖော်မတ်သည် အသုံးပြုသူမှ ဆုံးဖြတ်သည်။

နိမ့်သောမှတ်ဉာဏ်နှင့် page00.page03 အထက်မှတ်ဉာဏ်၏အသေးစိတ်ဖော်ပြချက် ကျေးဇူးပြု၍ SFF-8436 စာရွက်စာတမ်းကိုကြည့်ပါ။

•Soft Control နှင့် Status Functions အတွက် အချိန်ကိုက်ခြင်း။

| ကန့်သတ်ချက် | သင်္ကေတ | မက်တယ်။ | ယူနစ် | အခြေအနေများ |

| စတင်လုပ်ဆောင်ချိန် | t_init | ၂၀၀၀ | ms | ပါဝါဖွင့်ခြင်း 1 မှနေ၍ ပူသောပလပ် သို့မဟုတ် မော်ဂျူးအား အပြည့်အဝလုပ်ဆောင်နိုင်သည်အထိ ပြန်လည်သတ်မှတ်ရန် အနားတက်လာသည့်အချိန် |

| Init Assert Time ကို ပြန်လည်သတ်မှတ်ပါ။ | t_reset_init | 2 | μs | ပြန်လည်သတ်မှတ်ခြင်းကို ResetL pin တွင်ရှိသော အနိမ့်ဆုံးပြန်လည်သတ်မှတ်ချိန်ထက် ပိုရှည်သောအဆင့်ဖြင့် ထုတ်ပေးသည်။ |

| Serial Bus Hardware အဆင်သင့်ဖြစ်ချိန် | t_serial | ၂၀၀၀ | ms | 2-wire serial bus ပေါ်တွင် module မှဒေတာပေးပို့ခြင်းကိုတုံ့ပြန်သည်အထိ power on1 မှအချိန် |

| Monitor Data အဆင်သင့်ဖြစ်ပါပြီ။အချိန် | t_data | ၂၀၀၀ | ms | ပါဝါ on1 မှ ဒေတာ အဆင်သင့်မဖြစ်သေးသည့်အချိန်၊ Byte 2 ၏ ဘစ် 0၊ ဖျက်သိမ်းထားပြီး IntL မှ အတည်ပြုထားသည် |

| အခိုင်အမာအချိန်ကို ပြန်လည်သတ်မှတ်ပါ။ | t_reset လုပ်ပါ။ | ၂၀၀၀ | ms | မော်ဂျူးကို အပြည့်အဝလုပ်ဆောင်နိုင်သည်အထိ ResetL ပင်အစွန်းမှ တက်လာသည့်အချိန် |

| LPMode အခိုင်အမာအချိန် | ton_LPMode | ၁၀၀ | μs | LPMode (Vin:LPMode =Vih) ၏ အတည်ပြုချက်မှ module ပါဝါသုံးစွဲမှုသည် ပါဝါအဆင့် နိမ့်ကျသည့်အချိန်အထိ |

| IntL အခိုင်အမာအချိန် | ton_IntL | ၂၀၀ | ms | IntL စတင်ဖြစ်ပေါ်သည့် အခြေအနေမှ Vout:IntL = Vol |

| IntL Deassert အချိန် | toff_IntL | ၅၀၀ | μs | toff_IntL 500 μs ဆက်စပ်အလံ၏ read3 လည်ပတ်မှုကို ရှင်းလင်းသည့်အချိန်မှ Vout:IntL = Voh အထိ။၎င်းတွင် Rx LOS၊ Tx Fault နှင့် အခြား flag bits များအတွက် deassert အချိန်များ ပါဝင်သည်။ |

| Rx LOS Assert Time | ton_los | ၁၀၀ | ms | အချိန်ကို Rx LOS ပြည်နယ်မှ Rx LOS ဘစ်သို့ သတ်မှတ်ပြီး IntL က အတည်ပြုထားသည်။ |

| အလံ အခိုင်အမာ အချိန် | ton_flag | ၂၀၀ | ms | အလံစတင်ဖြစ်ပေါ်သည့်အခြေအနေမှ ဆက်စပ်အလံဘစ်သတ်မှတ်မှုအထိ အချိန်နှင့် IntL က အခိုင်အမာဖော်ပြခဲ့သည်။ |

| Mask Assert Time | ton_mask | ၁၀၀ | ms | ဆက်စပ် IntL အခိုင်အမာပြောဆိုမှုကို ဟန့်တားသည်အထိ mask bit set4 မှ အချိန် |

| Mask De-assert Time | toff_mask | ၁၀၀ | ms | ဆက်စပ် IntlL လုပ်ဆောင်ချက် ပြန်လည်စတင်သည်အထိ Mask bit cleared4 မှ အချိန် |

| ModSelL အခိုင်အမာအချိန် | ton_ModSelL | ၁၀၀ | μs | ModSelL ၏အခိုင်အမာပြောဆိုမှုမှအချိန်သည် 2-ဝါယာကြိုးအမှတ်စဉ်ဘတ်စ်ပေါ်တွင်ဒေတာပေးပို့ခြင်းကို module မှတုံ့ပြန်သည်အထိအချိန် |

| ModSelL Deassert အချိန် | toff_ModSelL | ၁၀၀ | μs | ModSelL ကို ဖြုတ်ချပြီးချိန်မှ module သည် 2-wire serial bus မှ data transmission ကို တုံ့ပြန်ခြင်းမရှိသည့်တိုင်အောင် အချိန် |

| Power_over-ride သို့မဟုတ်အတည်ပြုချိန်ကို ပါဝါသတ်မှတ်ပါ။ | ton_Pdown | ၁၀၀ | ms | မော်ဂျူးပါဝါသုံးစွဲမှု ပါဝါအဆင့်နိမ့်သည့်အထိ P_Down bit set 4 မှ အချိန် |

| Power_over-ride သို့မဟုတ် Power-set De-assert Time | toff_Pdown | ၃၀၀ | ms | Module အပြည့်အဝလုပ်ဆောင်နိုင်သည်အထိ P_Down bit cleared4 မှ အချိန် |

မှတ်ချက်:

1. ပါဝါဖွင့်ခြင်းကို ထောက်ပံ့ရေးဗို့အားများရောက်ရှိပြီး အနိမ့်ဆုံးသတ်မှတ်ထားသောတန်ဖိုးတွင် သို့မဟုတ် အထက်တွင်ရှိနေသည့်အခါ လက်ငင်းအဖြစ် သတ်မှတ်သည်။

2. အပြည့်အဝလုပ်ဆောင်နိုင်သော အချက်အလက်ကို အဆင်သင့်မဖြစ်သေးသော bit၊ bit 0 byte 2 de-asserted ကြောင့် IntL asserted အဖြစ် သတ်မှတ်သည်။

3. ဖတ်ပြီးသော အရောင်းအ၀ယ်ရပ်တန့်ပြီးနောက် နာရီအစွန်းကျသွားခြင်းမှ တိုင်းတာသည်။

4. ရေးမှတ်ထားသော အရောင်းအ၀ယ်ရပ်တန့်ပြီးနောက် နာရီအစွန်းကျသွားခြင်းမှ တိုင်းတာသည်။

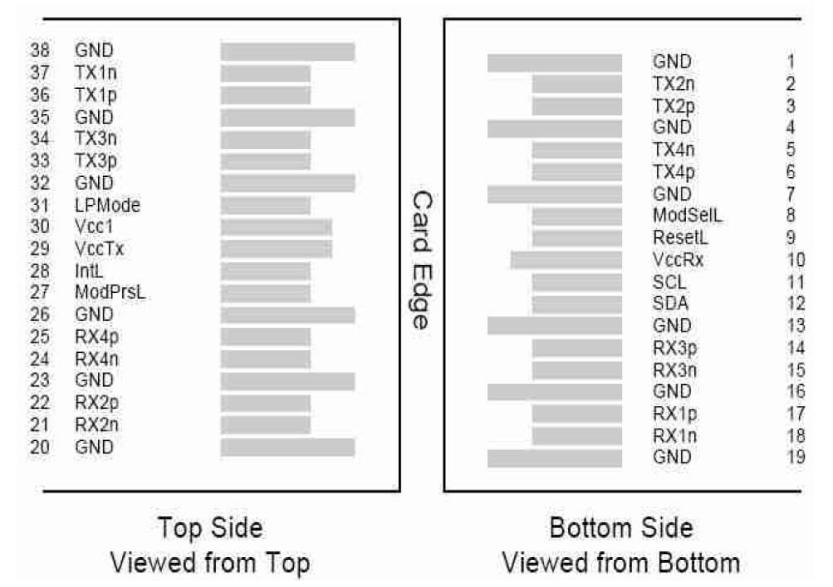

•Pin Assignment

Host Board Connector ၏ Diagram သည် Pin နံပါတ်များနှင့် အမည်ကို ပိတ်ဆို့သည်။

• ပင်ထိုးပါ။ဖော်ပြချက်

| တံ | ယုတ္တိဗေဒ | သင်္ကေတ | အမည်/ဖော်ပြချက် | Ref. |

| 1 |

| GND | မြေပြင် | 1 |

| 2 | CML-I | Tx2n | Transmitter သည် Inverted Data Input ဖြစ်သည်။ |

|

| ၃ | CML-I | Tx2p | Transmitter Non-Inverted Data အထွက် |

|

| 4 |

| GND | မြေပြင် | 1 |

| 5 | CML-I | Tx4n | Transmitter သည် Inverted Data Output ဖြစ်သည်။ |

|

| 6 | CML-I | Tx4p | Transmitter Non-Inverted Data Output |

|

| 7 |

| GND | မြေပြင် | 1 |

| 8 | LVTTL-I | ModSelL | Module ကို ရွေးပါ။ |

|

| 9 | LVTTL-I | ResetL | Module ကို ပြန်လည်သတ်မှတ်ပါ။ |

|

| 10 |

| VccRx | +3.3V Power Supply လက်ခံကိရိယာ | 2 |

| 11 | LVCMOS-I/O | SCL | 2-Wire Serial Interface နာရီ |

|

| 12 | LVCMOS-I/O | SDA | 2-Wire Serial Interface Data |

|

| 13 |

| GND | မြေပြင် | 1 |

| 14 | CML-O | Rx3p | လက်ခံသူသည် ဒေတာအထွက်ကို ပြောင်းပြန်လှန်ထားသည်။ |

|

| 15 | CML-O | Rx3n | လက်ခံသူသည် ပြောင်းပြန်မဟုတ်သော ဒေတာ ထုတ်ပေးသည်။ |

|

| 16 |

| GND | မြေပြင် | 1 |

| 17 | CML-O | Rx1p | လက်ခံသူသည် ဒေတာအထွက်ကို ပြောင်းပြန်လှန်ထားသည်။ |

|

| 18 | CML-O | Rx1n | လက်ခံသူသည် ပြောင်းပြန်မဟုတ်သော ဒေတာ ထုတ်ပေးသည်။ |

|

| 19 |

| GND | မြေပြင် | 1 |

| 20 |

| GND | မြေပြင် | 1 |

| 21 | CML-O | Rx2n | လက်ခံသူသည် ဒေတာအထွက်ကို ပြောင်းပြန်လှန်ထားသည်။ |

|

| 22 | CML-O | Rx2p | လက်ခံသူသည် ပြောင်းပြန်မဟုတ်သော ဒေတာ ထုတ်ပေးသည်။ |

|

| 23 |

| GND | မြေပြင် | 1 |

| 24 | CML-O | Rx4n | လက်ခံသူသည် ဒေတာအထွက်ကို ပြောင်းပြန်လှန်ထားသည်။ |

|

| 25 | CML-O | Rx4p | လက်ခံသူသည် ပြောင်းပြန်မဟုတ်သော ဒေတာ ထုတ်ပေးသည်။ |

|

| 26 |

| GND | မြေပြင် | 1 |

| 27 | LVTTL-O | ModPrsL | Module Present |

|

| 28 | LVTTL-O | IntL | နှောက်ယှက်သည်။ |

|

| 29 |

| VccTx | +3.3V Power Supply Transmitter | 2 |

| 30 |

| Vcc1 | +3.3V ပါဝါထောက်ပံ့မှု | 2 |

| 31 | LVTTL-I | LPMode | ပါဝါမုဒ် |

|

| ၃၂ |

| GND | မြေပြင် | 1 |

| 33 | CML-I | Tx3p | Transmitter သည် Inverted Data Output ဖြစ်သည်။ |

|

| 34 | CML-I | Tx3n | Transmitter Non-Inverted Data Output |

|

| 35 |

| GND | မြေပြင် | 1 |

| 36 | CML-I | Tx1p | Transmitter သည် Inverted Data Output ဖြစ်သည်။ |

|

| 37 | CML-I | Tx1n | Transmitter Non-Inverted Data Output |

|

| 38 |

| GND | မြေပြင် | 1 |

မှတ်စုများ-

- GND သည် QSFP မော်ဂျူးများအတွက် ဘုံတစ်ခုတည်းနှင့် ထောက်ပံ့မှု(ပါဝါ) သင်္ကေတဖြစ်ပြီး၊ အားလုံးသည် QSFP မော်ဂျူးအတွင်းတွင်သာမန်ဖြစ်ပြီး မော်ဂျူးဗို့အားအားလုံးကို ရည်ညွှန်းကာ ဤအလားအလာကို အခြားနည်းဖြင့် မှတ်သားထားသည်။၎င်းတို့ကို host board signal ဘုံ ground plane သို့ တိုက်ရိုက်ချိတ်ဆက်ပါ။လေဆာအထွက်အား TDIS >2.0V တွင် ပိတ်ထားသည် သို့မဟုတ် TDIS <0.8V တွင် ဖွင့်ထားသည်

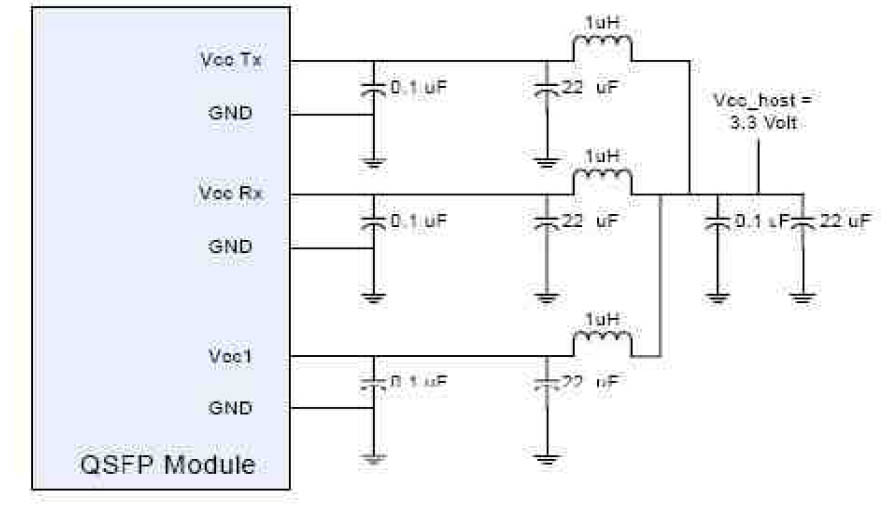

- VccRx၊ Vcc1 နှင့် VccTx တို့သည် လက်ခံသူနှင့် transmitter ပါဝါပေးသွင်းသူများဖြစ်ပြီး တစ်ပြိုင်နက် အသုံးချရမည်ဖြစ်သည်။အကြံပြုထားသော host board power supply filtering ကို အောက်တွင် ပြထားသည်။VccRx၊ Vcc1 နှင့် VccTx သည် မည်သည့်ပေါင်းစပ်မှုတွင်မဆို QSFP transceiver module အတွင်းအတွင်းပိုင်း ချိတ်ဆက်နိုင်ပါသည်။connector pin များကို တစ်ခုချင်းစီတွင် အများဆုံး 500mA အတွက် အဆင့်သတ်မှတ်ထားသည်။

•အကြံပြုထားသော Circuit

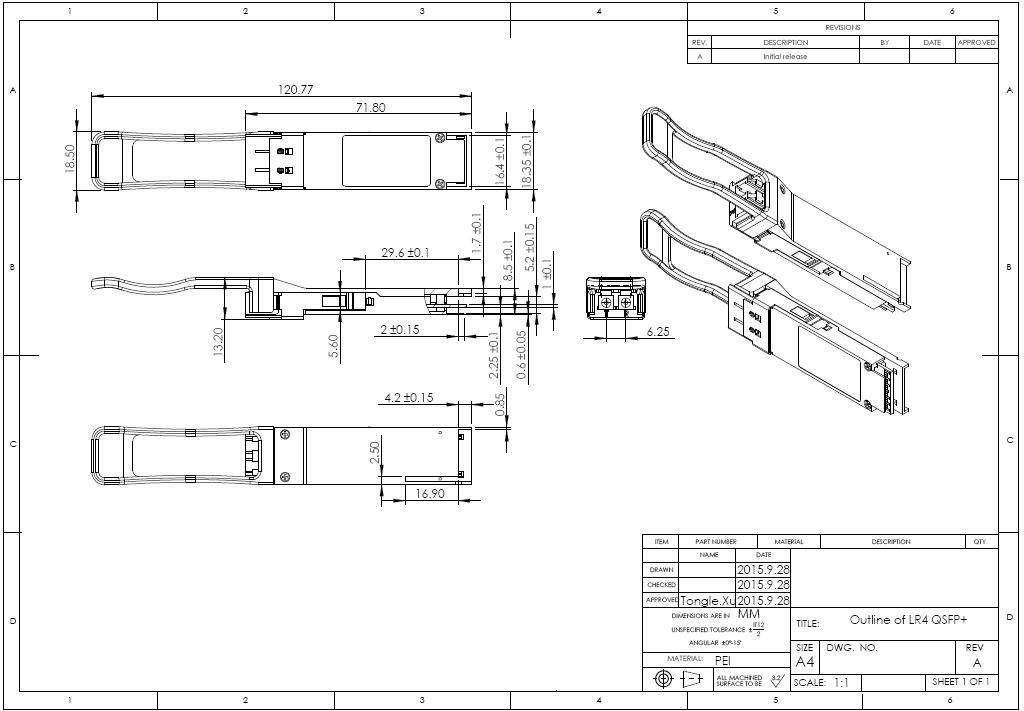

စက်ပိုင်းဆိုင်ရာ အတိုင်းအတာများ